www.ti.com

2.5MemoryWidthandByteAlignment

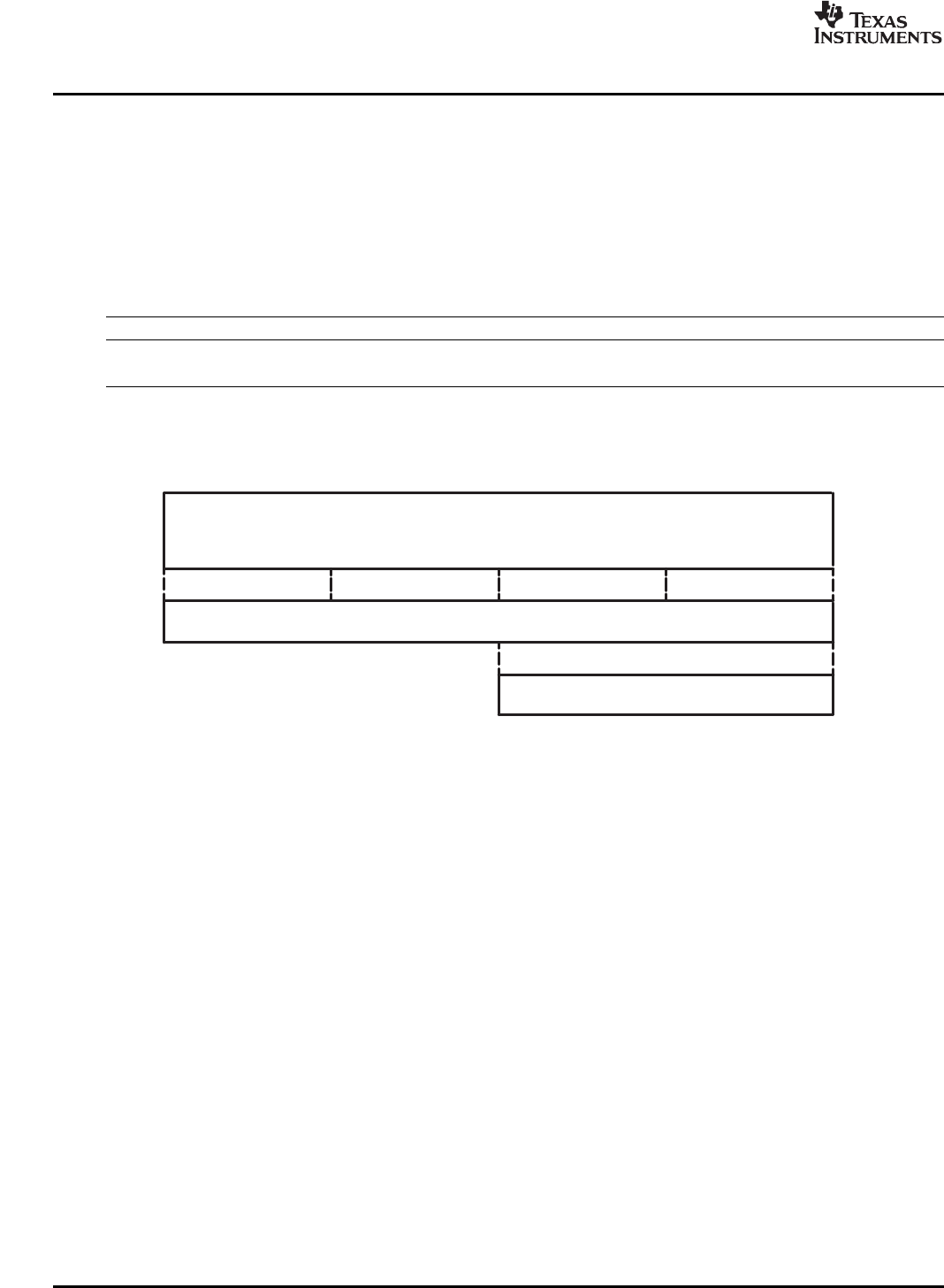

DDR2 memory controller data bus

DDR_D[31:24]

DDR_D[23:16] DDR_D[15:8] DDR_D[7:0]

32-bit memory device

16-bit memory device

PeripheralArchitecture

TheDDR2memorycontrollersupportsmemorywidthsof16bitsand32bits.Table5summarizesthe

addressablememoryrangesontheDDR2memorycontroller.Seethedevice-specificdatamanualforthe

memorywidthsthataresupported.

Figure11showsthebytelanesusedontheDDR2memorycontroller.Theexternalmemoryisalways

right-alignedonthedatabus.

Table5.AddressableMemoryRanges

MemoryWidthMaximumaddressablebytesperCSspaceDescription

×16128MbytesHalfwordaddress

×32256MbytesWordaddress

Figure11.ByteAlignment

DDR2MemoryController 20SPRU986B–November2007

SubmitDocumentationFeedback