www.ti.com

4.4SDRAMTimingRegister(SDTIMR)

DDR2MemoryControllerRegisters

TheSDRAMtimingregister(SDTIMR)configurestheDDR2memorycontrollertomeetmanyoftheAC

timingspecificationoftheDDR2memory.TheSDTIMRregisterisprogrammableonlywhenthe

TIMUNLOCKbitissetto1intheSDBCR.NotethatDDR_CLKisequaltotheperiodoftheDDR_CLK

signal.SeetheDDR2memorydatasheetforinformationontheappropriatevaluestoprogrameachfield.

TheSDTIMRisshowninFigure22anddescribedinTable28.

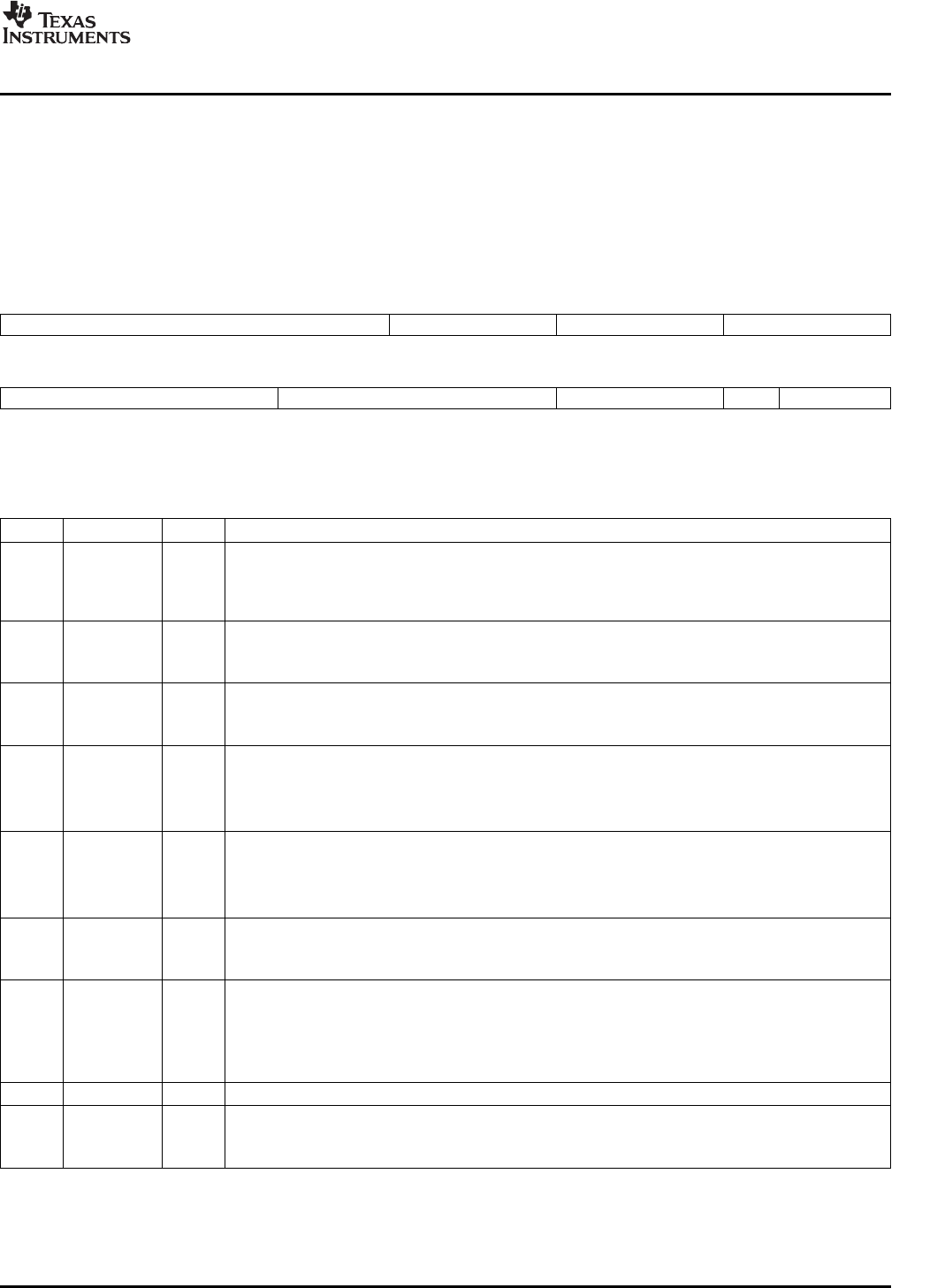

Figure22.SDRAMTimingRegister(SDTIMR)

3125242221191816

T_RFCT_RPT_RCDT_WR

R/W-1AhR/W-5hR/W-5hR/W-3h

151110653210

T_RAST_RCT_RRDRsvdT_WTR

R/W-9hR/W-EhR/W-3hR-0R/W-3h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table28.SDRAMTimingRegister(SDTIMR)FieldDescriptions

BitFieldValueDescription

31-25T_RFC0-7FhSpecifiestheminimumnumberofDDR_CLKcyclesfromarefreshorloadmodecommandtoarefresh

oractivatecommand,minus1.Correspondstothet

rfc

ACtimingparameterintheDDR2datasheet.

Calculateby:

T_RFC=(t

rfc

/DDR_CLKperiod)-1

24-22T_RP0-7hSpecifiestheminimumnumberofDDR_CLKcyclesfromaprechargecommandtoarefreshoractivate

command,minus1.Correspondstothet

rp

ACtimingparameterintheDDR2datasheet.Calculateby:

T_RP=(t

rp

/DDR_CLKperiod)-1

21-19T_RCD0-7hSpecifiestheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoareadorwrite

command,minus1.Correspondstothet

rcd

ACtimingparameterintheDDR2datasheet.Calculateby:

T_RCD=(t

rcd

/DDR_CLKperiod)-1

18-16T_WR0-7hSpecifiestheminimumnumberofDDR_CLKcyclesfromthelastwritetransfertoaprecharge

command,minus1.Correspondstothet

wr

ACtimingparameterintheDDR2datasheet.Calculateby:

T_WR=(t

wr

/DDR_CLKperiod)-1

Whenthevalueofthisfieldischangedfromitspreviousvalue,theinitializationsequencewillbegin.

15-11T_RAS0-1FhSpecifiestheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoaprecharge

command,minus1.Correspondstothet

ras

ACtimingparameterintheDDR2datasheet.Calculateby:

T_RAS=(t

ras

/DDR_CLKperiod)-1

T_RASmustbegreaterthanorequaltoT_RCD.

10-6T_RC0-1FhSpecifiestheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoanactivate

command,minus1.Correspondstothet

rc

ACtimingparameterintheDDR2datasheet.Calculateby:

T_RC=(t

rc

/DDR_CLKperiod)-1

5-3T_RRD0-7hSpecifiestheminimumnumberofDDR_CLKcyclesfromanactivatecommandtoanactivatecommand

inadifferentbank,minus1.Correspondstothet

rrd

ACtimingparameterintheDDR2datasheet.

Calculateby:

T_RRD=(t

rrd

/DDR_CLKperiod)-1

Note:foran8bankDDR2devicethisfieldmustbeequalto((4×t

RRD

)+(2×t

CK

))/(4×t

CK

)-1.

2Reserved0Reserved

1-0T_WTR0-3hSpecifiestheminimumnumberofDDR_CLKcyclesfromthelastwritetoareadcommand,minus1.

Correspondstothet

wtr

ACtimingparameterintheDDR2datasheet.Calculateby:

T_WTR=(t

wtr

/DDR_CLKperiod)-1

SPRU986B–November2007DDR2MemoryController45

SubmitDocumentationFeedback