www.ti.com

2PeripheralArchitecture

2.1ClockControl

2.1.1ClockSource

DDR2

memory

controller

/2

PLLC2

/3

PLLC1

X2_CLKVCLK

DDR_CLK

DDR_CLK

PLL2_SYSCLK1

SYSCLK2

PeripheralArchitecture

ThissectiondescribesthearchitectureoftheDDR2memorycontrolleraswellashowitisstructuredand

howitworkswithinthecontextofthesystem-on-a-chip.TheDDR2memorycontrollercangluelessly

interfacetomoststandardDDR2SDRAMdevicesandsupportssuchfeaturesasself-refreshmodeand

prioritizedrefresh.Inaddition,itprovidesflexibilitythroughprogrammableparameterssuchastherefresh

rate,CASlatency,andmanySDRAMtimingparameters.Thefollowingsectionsincludedetailsonhowto

interfaceandproperlyconfiguretheDDR2memorycontrollertoperformreadandwriteoperationsto

externally-connectedDDR2SDRAMdevices.Also,Section3providesadetailedexampleofinterfacing

theDDR2memorycontrollertoacommonDDR2SDRAMdevice.

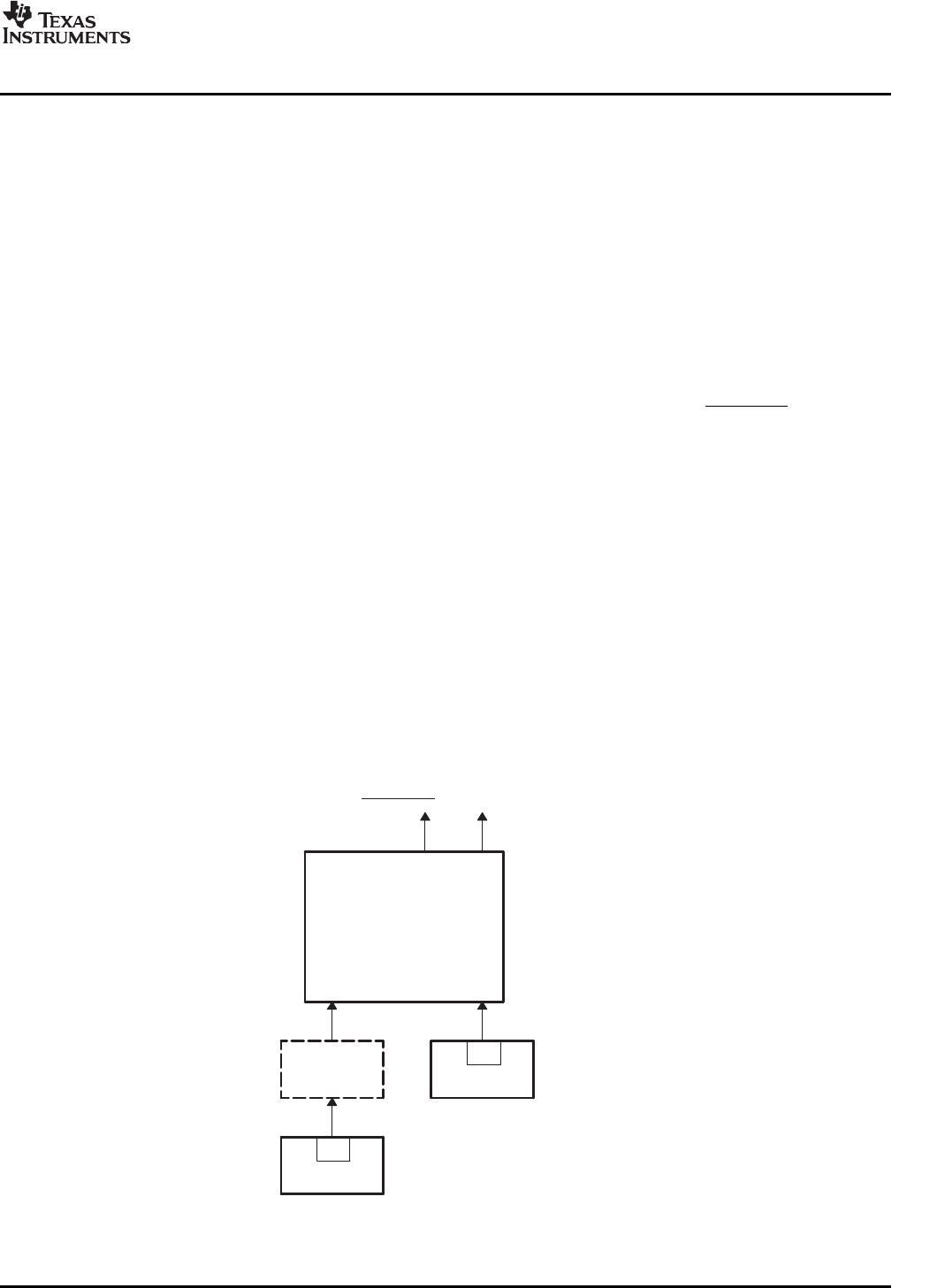

TheDDR2memorycontrollerreceivestwoinputclocksfrominternalclocksources,SYSCLK2and

PLL2_SYSCLK1(Figure2).SYSCLK2isadivided-downversionoftheDSPclock.PLL2_SYSCLK1

shouldbeconfiguredtoclockatthefrequencyofthedesireddatarate,orstatedsimilarly,itshould

operateattwicethefrequencyofthedesiredDDR2memoryclock.DDR_CLKandDDR_CLKarethetwo

outputclocksoftheDDR2memorycontrollerprovidingtheinterfaceclocktotheDDR2SDRAMmemory.

ThesetwoclocksoperateatafrequencyofPLL2_SYSCLK1/2.

SYSCLK2andPLL2_SYSCLK1aresourcedfromtwoindependentPLLs(Figure2).SYSCLK2issourced

fromPLLcontroller1(PLLC1)andPLL2_SYSCLK1issourcedfromPLLcontroller2(PLLC2).

SYSCLK2isclockedatafixeddividerratioofPLL1.Thisdividerisfixedat3,meaningSYSCLK2is

clockedatafrequencyofPLL1/3.OnceinsidetheDDR2memorycontroller,thissignaliscalledVCLK.

PLLC2hasaprogrammabledividerthatisusedtodivide-downtheoutputclockofPLL2.Thisdivider

shouldbeconfiguredsuchthatPLLC2suppliesthePLL2_SYSCLK1atthedesiredfrequency.For

example,ifa150-MHZDDR2interfaceclock(DDR_CLK)isdesired,thenPLLC2mustbeconfiguredto

generatea300-MHZclockonPLL2_SYSCLK1.OnceinsidetheDDR2memorycontroller,

PLL2_SYSCLK1iscalledX2_CLK.

Figure2.DDR2MemoryControllerClockBlockDiagram

SPRU986B–November2007DDR2MemoryController9

SubmitDocumentationFeedback