www.ti.com

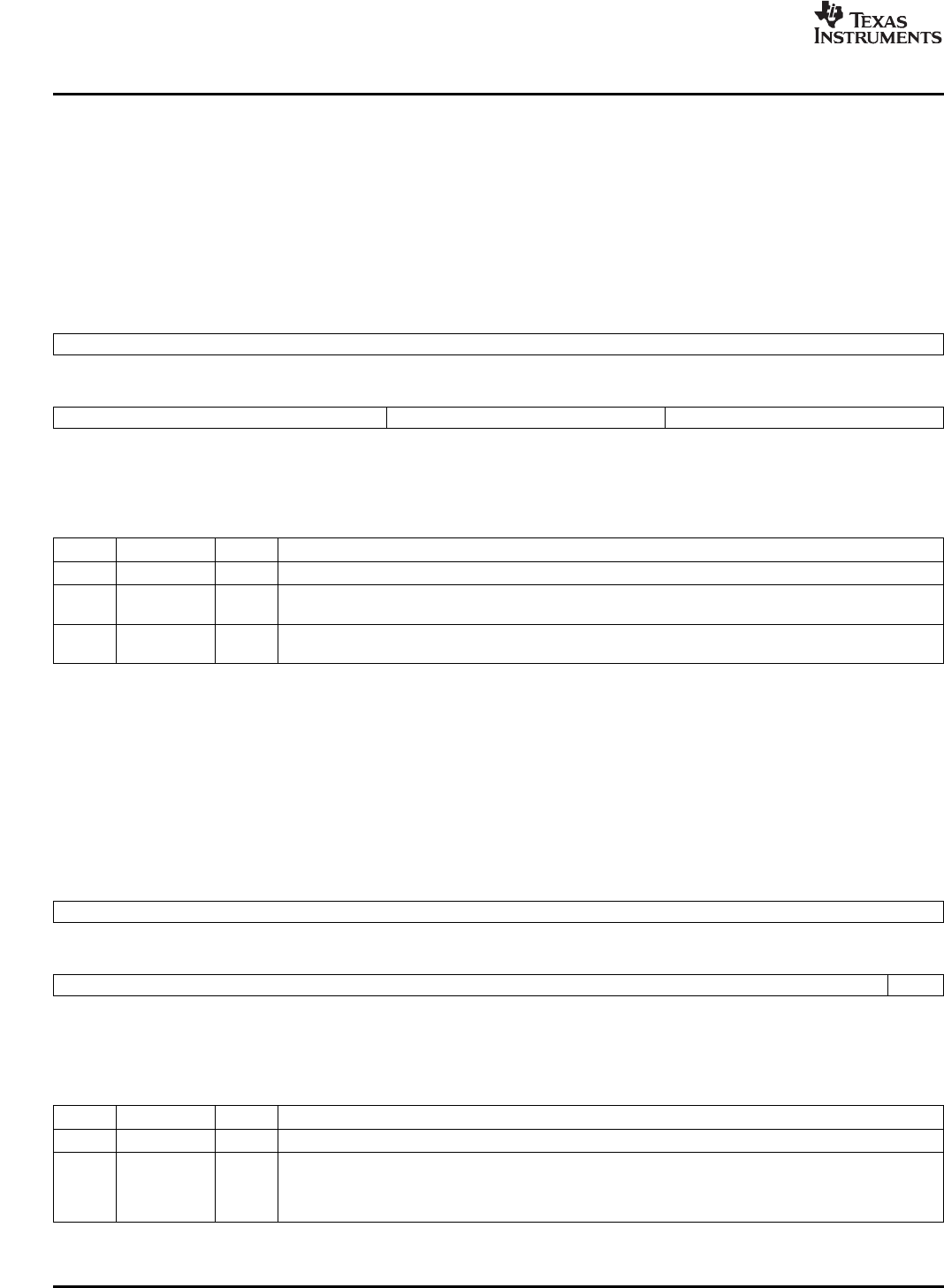

4.13DDRVTPRegister(DDRVTPR)

4.14DDRVTPEnableRegister(DDRVTPER)

DDR2MemoryControllerRegisters

TheDDRVTPregister(DDRVTPR)isusedinconjunctionwiththeVTPIOcontrolregister(VTPIOCR)to

calibratetheoutputimpedanceoftheDDR2memorycontrollerIOswithrespecttovoltage,temperature,

andprocess.Followingthecalibrationsequence,DDRVTPRcontainstheinformationneededtocalibrate

theimpedanceoftheIO.Oncethecalibrationsequencehascompleted,DDRVTPRshouldbereadand

thedatawrittentothePCHandNCHfieldsinVTPIOCR.TheDDRVTPRisshowninFigure31and

describedinTable37.

Figure31.DDRVTPRegister(DDRVTPR)

3116

Reserved

R-0

15109540

ReservedPCHNCH

R-0R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table37.DDRVTPRegister(DDRVTPR)FieldDescriptions

BitFieldValueDescription

31-10Reserved0Reserved.

9-5PCH0-1FhPchannelvalueforIOimpedancecalibration.FollowingtheVTPcalibrationsequence,thisvalueshould

bereadandwrittentothePCHfieldintheVTPIOcontrolregister(VTPIOCR).

4-0NCH0-1FhNchannelvalueforIOimpedancecalibration.FollowingtheVTPcalibrationsequence,thisvalue

shouldbereadandwrittentotheNCHfieldintheVTPIOcontrolregister(VTPIOCR).

TheDDRVTPenableregister(DDRVTPER)isusedtoenable/disableaccessestotheDDRVTPregister

(DDRVTPR).Writingavalueof1toDDRVTPERenablesaccessestoDDRVTPRandwritingavalueof0

disablesaccessestoDDRVTPR.TheDDRVTPERisshowninFigure32anddescribedinTable38.

Figure32.DDRVTPEnableRegister(DDRVTPER)

3116

Reserved

R-0

1510

ReservedEN

R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table38.DDRVTPEnableRegister(DDRVTPER)FieldDescriptions

BitFieldValueDescription

31-1Reserved0Reserved.Alwayswrite0tothesebits.

0ENDDRVTPRaccessenable.

0AccesstoDDRVTPRisdisabled.

1AccesstoDDRVTPRisenabled.

DDR2MemoryController 54SPRU986B–November2007

SubmitDocumentationFeedback