www.ti.com

4.2SDRAMBankConfigurationRegister(SDBCR)

DDR2MemoryControllerRegisters

TheSDRAMbankconfigurationregister(SDBCR)containsfieldsthatprogramtheDDR2memory

controllertomeetthespecificationoftheattachedDDR2memory.ThesefieldsconfiguretheDDR2

memorycontrollertomatchthedatabuswidth,CASlatency,numberofinternalbanks,andpagesizeof

theattachedDDR2memory.TheSDBCRisshowninFigure20anddescribedinTable26.Writingtothe

DDRDRIVE,CL,IBANK,andPAGESIZEbitfieldswillcausetheDDR2memorycontrollertostartthe

DDR2SDRAMinitializationsequence.

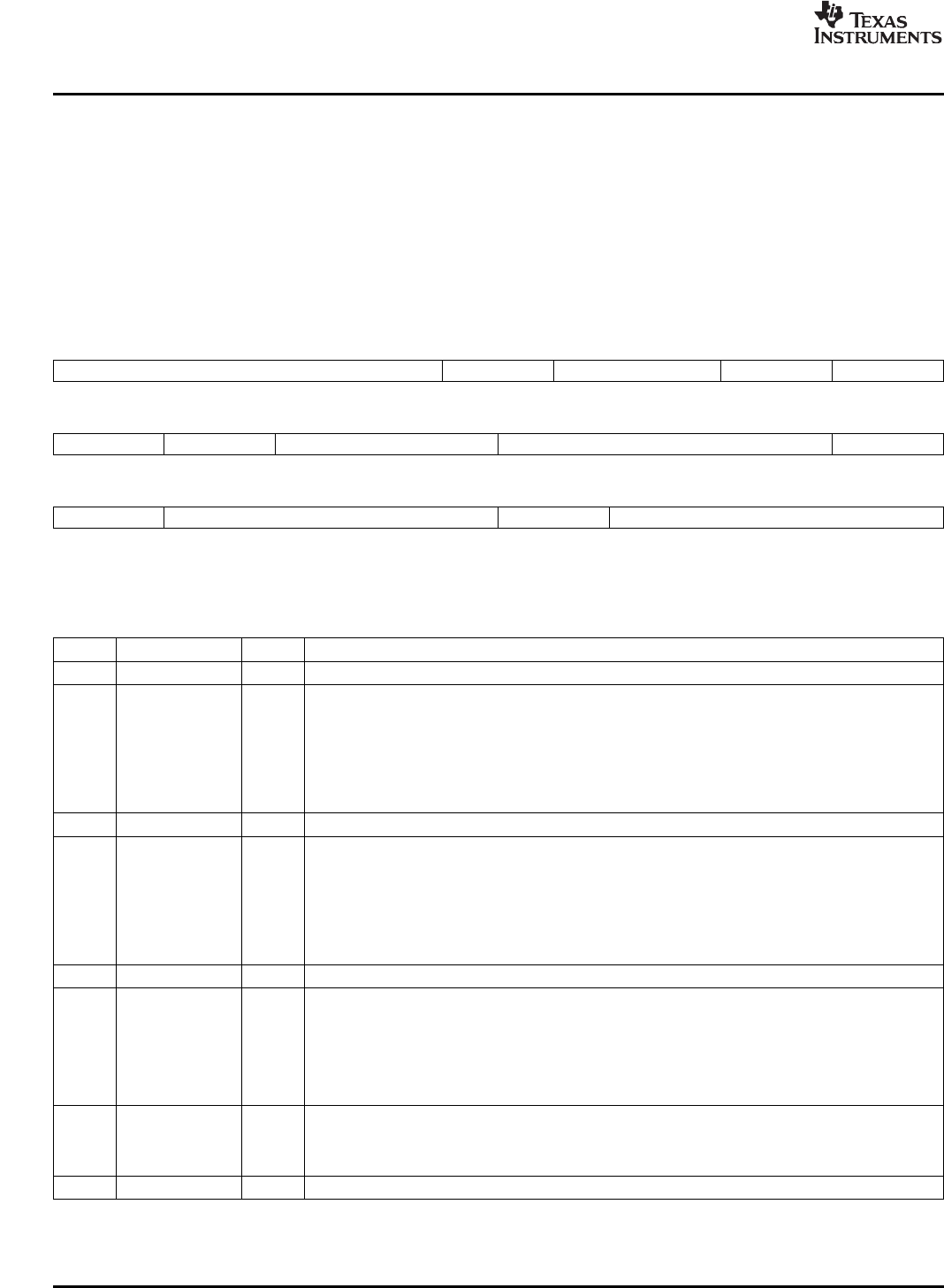

Figure20.SDRAMBankConfigurationRegister(SDBCR)

3124232219181716

ReservedBOOTUNLOCKReservedDDRDRIVEReserved

R/W-1R/W-0R/W-2hR/W-1R-3h

151413121198

TIMUNLOCKNMReservedCLReserved

R/W-0R/W-0R-0R/W-5hR-0

764320

ReservedIBANKReservedPAGESIZE

R-0R/W-2hR-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table26.SDRAMBankConfigurationRegister(SDBCR)FieldDescriptions

BitFieldValueDescription

31-24Reserved0Reserved.Alwayswriteavalueof0tothesebits.

23BOOTUNLOCKBootunlock.ControlsthewritepermissionsettingsfortheDDRDRIVEbit.Tochangethe

DDRDRIVEbitvalue,usethefollowingsequence:

1.Writea1totheBOOTUNLOCKbit.

2.Writea0totheBOOTUNLOCKbitalongwiththedesiredvalueoftheDDRDRIVEbit.

0DDRDRIVEbitmaynotbechanged

1DDRDRIVEbitmaybechanged

22-19Reserved2hReserved.Alwayswriteavalueof2htothesebits.

18DDRDRIVEDDR2SDRAMdrivestrength.ConfigurestheoutputdriverimpedancecontrolvalueoftheDDR2

SDRAMmemory.TochangetheDDRDRIVEbitvalue,usethefollowingsequence:

1.Writea1totheBOOTUNLOCKbit.

2.Writea0totheBOOTUNLOCKbitalongwiththedesiredvalueoftheDDRDRIVEbit.

0Normaldrivestrength.

1Weakdrivestrength.

17-16Reserved3hReserved.Alwayswriteavalueof3htothesebits.

15TIMUNLOCKTimingunlock.ControlsthewritepermissionsettingsfortheSDRAMtimingregisterandSDRAM

timingregister2.

0RegisterfieldsintheSDRAMtimingregister(SDTIMR)andtheSDRAMtimingregister2

(SDTIMR2)maynotbechanged.

1RegisterfieldsintheSDRAMtimingregister(SDTIMR)andtheSDRAMtimingregister2

(SDTIMR2)maybechanged.

14NMDDR2databuswidth.

032-bitbuswidth.

116-bitbuswidth

13-12Reserved0Reserved

42DDR2MemoryControllerSPRU986B–November2007

SubmitDocumentationFeedback