www.ti.com

2.4ProtocolDescription(s)

PeripheralArchitecture

TheDDR2memorycontrollersupportstheDDR2SDRAMcommandslistedinTable3.Table4showsthe

signaltruthtablefortheDDR2SDRAMcommands.

Table3.DDR2SDRAMCommands

CommandFunction

ACTVActivatestheselectedbankandrow.

DCABPrechargeallcommand.Deactivates(precharges)allbanks.

DEACPrechargesinglecommand.Deactivates(precharges)asinglebank.

DESELDeviceDeselect.

EMRSExtendedModeRegisterset.Allowsalteringthecontentsofthemoderegister.

MRSModeregisterset.Allowsalteringthecontentsofthemoderegister.

NOPNooperation.

PowerDownPowerdownmode.

READInputsthestartingcolumnaddressandbeginsthereadoperation.

READwithInputsthestartingcolumnaddressandbeginsthereadoperation.Thereadoperationisfollowedbya

autoprechargeprecharge.

REFRAutorefreshcycle.

SLFREFRSelf-refreshmode.

WRTInputsthestartingcolumnaddressandbeginsthewriteoperation.

WRTwithInputsthestartingcolumnaddressandbeginsthewriteoperation.Thewriteoperationisfollowedbya

autoprechargeprecharge.

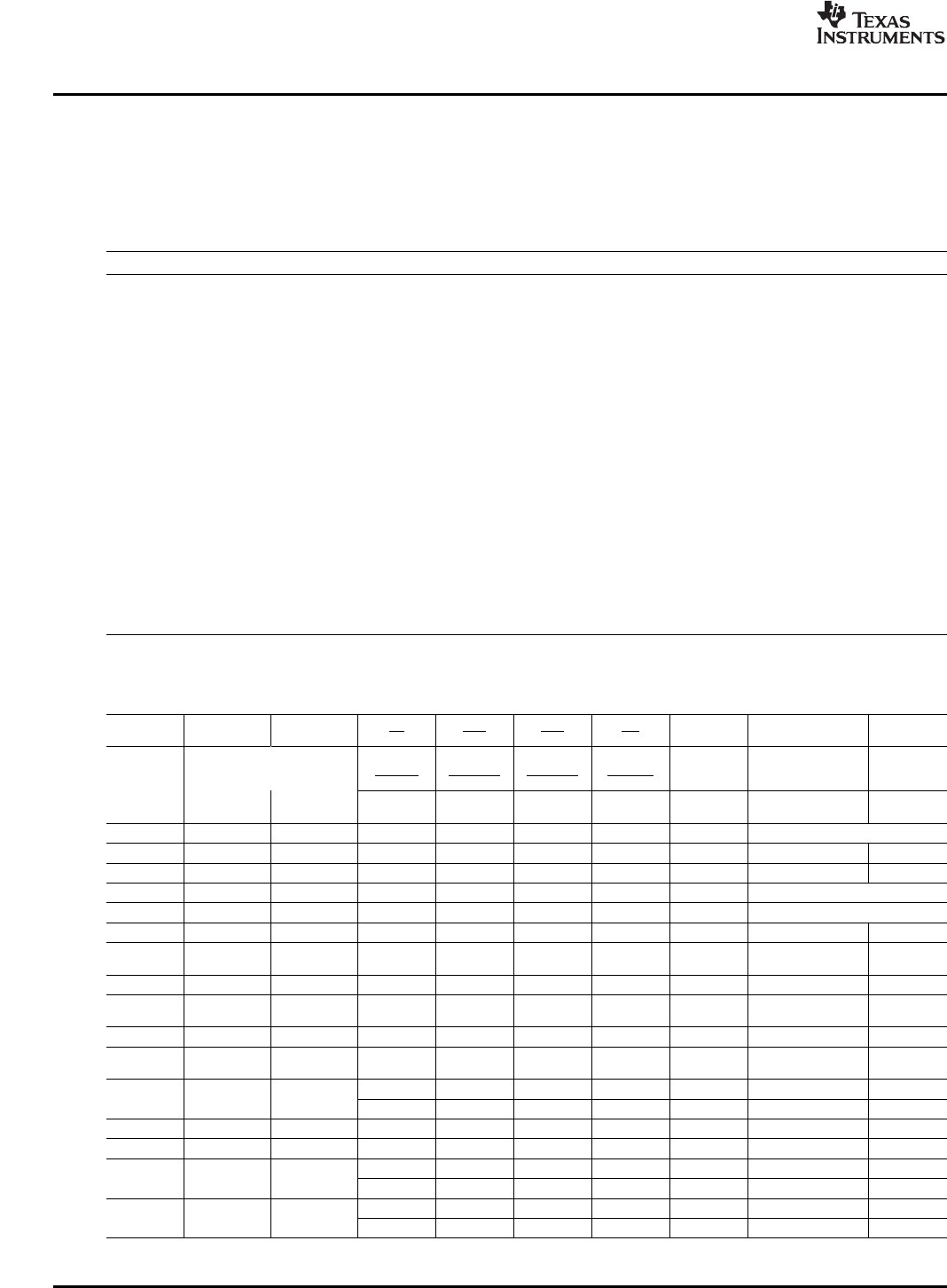

Table4.TruthTableforDDR2SDRAMCommands

DDR2

SDRAM:CKECSRASCASWEBA[2:0]A[12:11,9:0]A10

DDR2

memory

controller:DDR_CKEDDR_CSDDR_RASDDR_CASDDR_WEDDR_BA[2:0]DDR_A[12:11,9:0]DDR_A[10]

Previous

CyclesCurrentCycle

ACTVHHLLHHBankRowAddress

DCABHHLLHLXXL

DEACHHLLHLBankXL

MRSHHLLLLBAOPCode

EMRSHHLLLLBAOPCode

READHHLHLHBAColumnAddressL

READwithHHLHLHBAColumnAddressH

precharge

WRTHHLHLLBAColumnAddressL

WRTwithHHLHLLBAColumnAddressL

precharge

REFRHHLLLHXXX

SLFREFRHLLLLHXXX

entry

SLFREFRLHHXXXXXX

exit

LHHHXXX

NOPHXLHHHXXX

DESELHXHXXXXXX

PowerDownHLHXXXXXX

entry

LHHHXXX

PowerDownLHHXXXXXX

exit

LHHHXXX

12DDR2MemoryControllerSPRU986B–November2007

SubmitDocumentationFeedback