www.ti.com

DDR2MemoryControllerRegisters

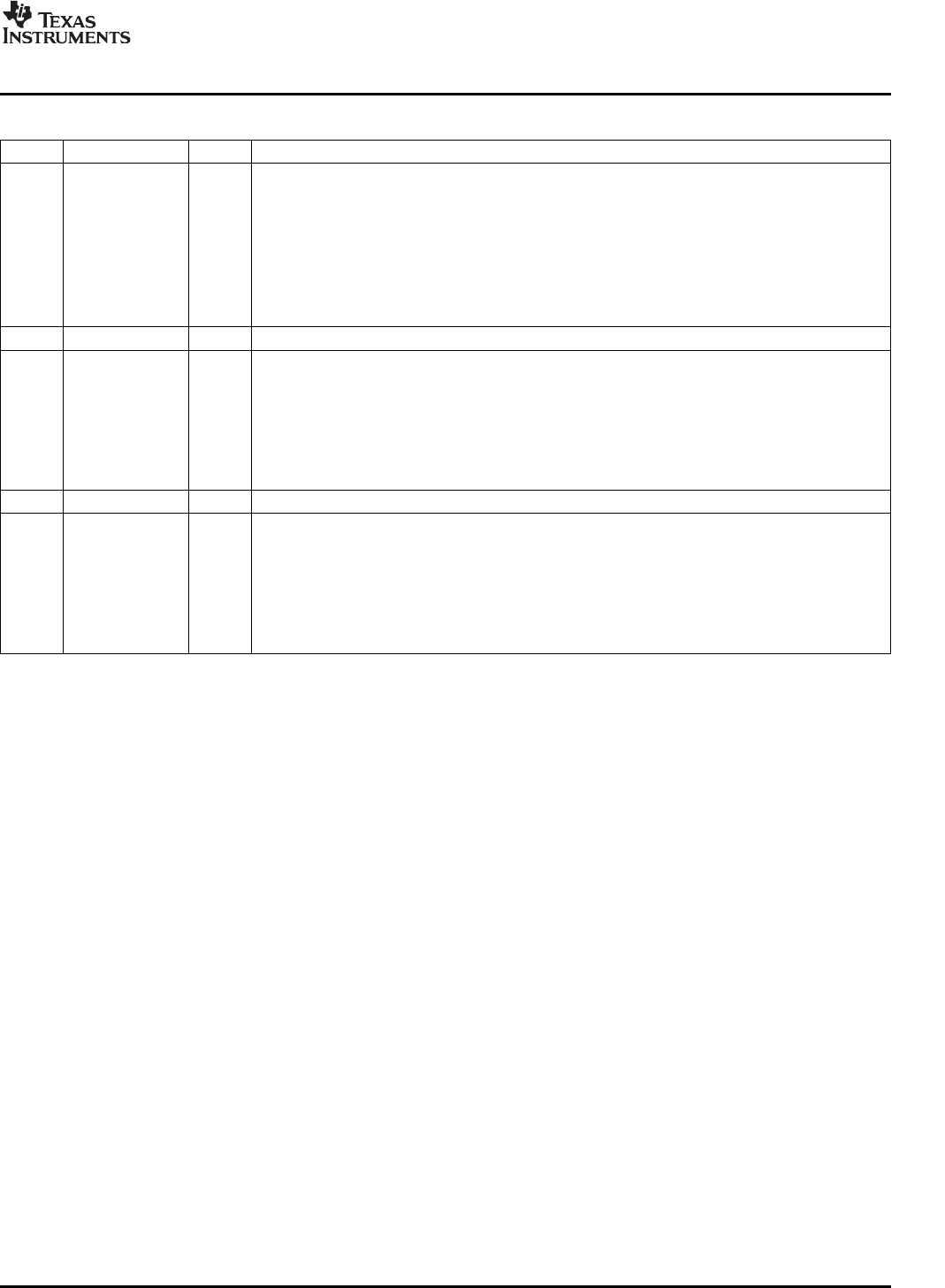

Table26.SDRAMBankConfigurationRegister(SDBCR)FieldDescriptions(continued)

BitFieldValueDescription

11-9CL0-7hCASlatency.

0-1hReserved

2hCASlatencyof2

3hCASlatencyof3

4hCASlatencyof4

5hCASlatencyof5

6h-7hReserved

8-7Reserved0Reserved

6-4IBANK0-7hInternalDDR2banksetup.DefinesthenumberofinternalbanksontheexternalDDR2memory.

01bank

1h2banks

2h4banks

3h8banks

4h-7hReserved

3Reserved0Reserved.Alwayswritea0tothisbit.

2-0PAGESIZE0-7hDDR2pagesize.DefinesthepagesizeofeachpageoftheexternalDDR2memory.

0256-wordpagerequiring8columnaddressbits.

1h512-wordpagerequiring9columnaddressbits.

2h1024-wordpagerequiring10columnaddressbits.

3h2048-wordpagerequiring11columnaddressbits.

4h-7hReserved

SPRU986B–November2007DDR2MemoryController43

SubmitDocumentationFeedback