www.ti.com

2.4.5Write(WRT)Command

DDR_CLK

DDR_CKE

DDR_CS

DDR_WE

DDR_CAS

DDR_DQM[3:0]

DDR_D[31:0]

DDR_A[12:0]

DDR_RAS

DDR_DQS[3:0]

COL

BANK

DDR_A[10]

DDR_BA[2:0]

DQM7

Sample

D0 D1 D2 D3 D4 D5 D6 D7

DQM1 DQM2 DQM3 DQM4 DQM5 DQM6 DQM8

Write Latency

DDR_CLK

PeripheralArchitecture

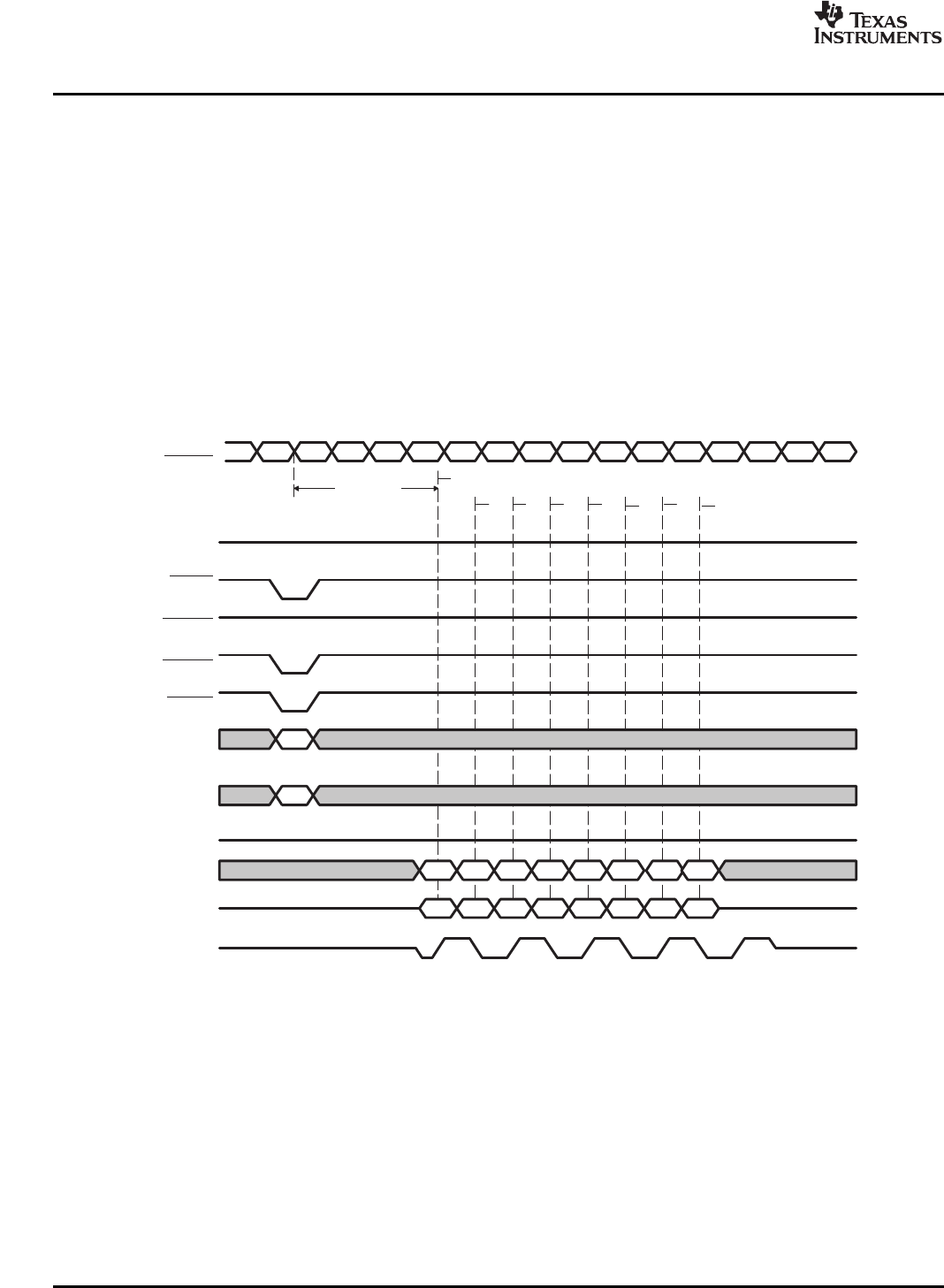

PriortoaWRTcommand,thedesiredbankandrowareactivatedbytheACTVcommand.Followingthe

WRTcommand,awritelatencyisincurred.WritelatencyisequaltoCASlatencyminus1.Allwriteshave

aburstlengthof8.TheuseoftheDDR_DQMoutputsallowsbyteandhalfwordwritestobeexecuted.

Figure9showsthetimingforawriteontheDDR2memorycontroller.

Ifthetransferrequestisforlessthan8words,dependingontheschedulingresultandthepending

commands,theDDR2memorycontrollercan:

•MaskouttheadditionaldatausingDDR_DQMoutputs

•Terminatethewriteburstandstartanewwriteburst

TheDDR2memorycontrollerdoesnotperformtheDEACcommanduntilpageinformationbecomes

invalid.

Figure9.DDR2WRTCommand

DDR2MemoryController 18SPRU986B–November2007

SubmitDocumentationFeedback