www.ti.com

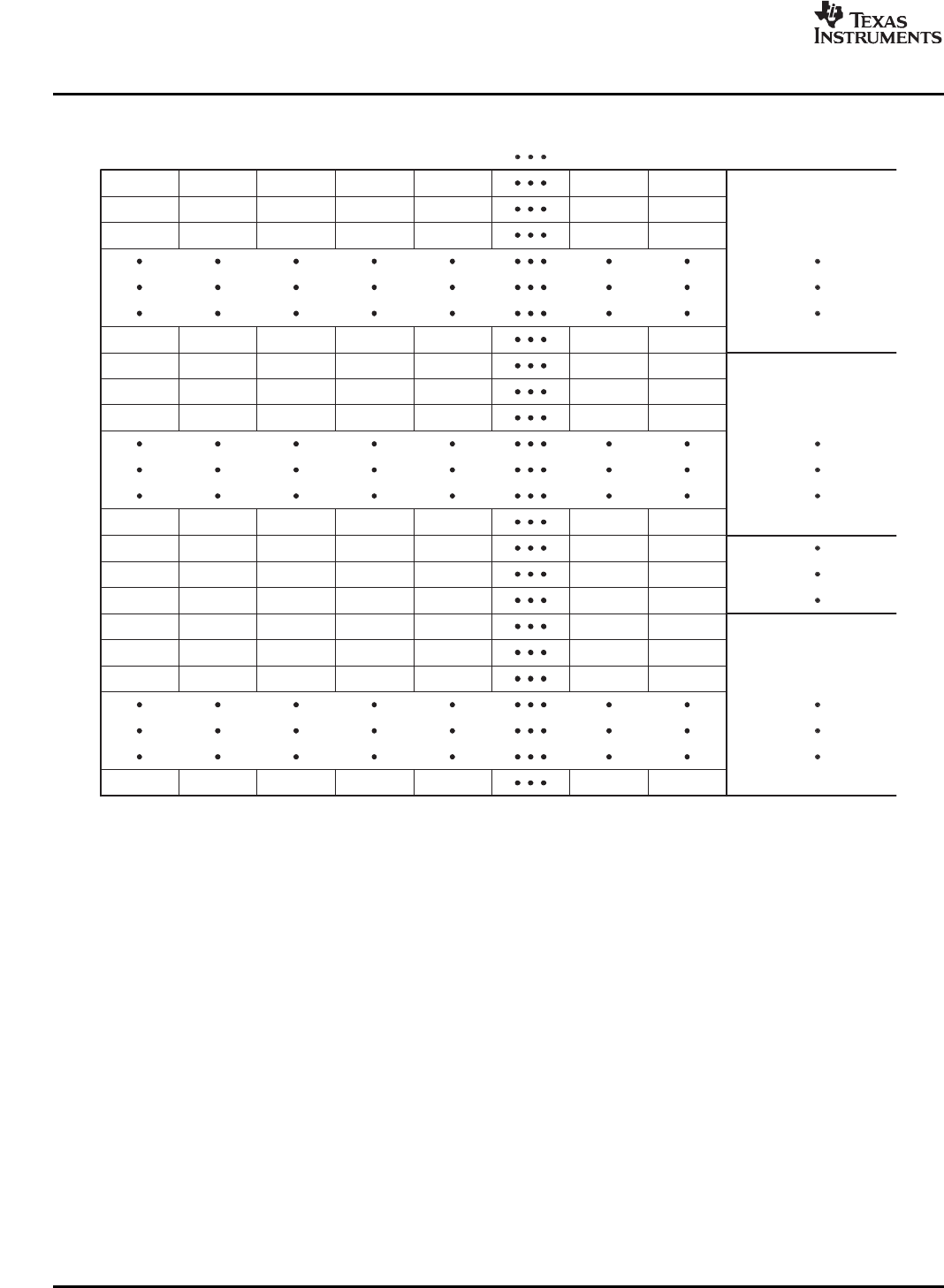

Col. 0 Col. 1 Col. 2 Col. 3 Col. 4 Col. M−1 Col. M

Row 0, bank 0

Row 0, bank 1

Row 0, bank 2

Row 0, bank P

Row 1, bank 1

Row 1, bank 0

Row 1, bank 2

Row 1, bank P

Row N, bank 2

Row N, bank 1

Row N, bank 0

Row N, bank P

PeripheralArchitecture

Figure12.LogicalAddress-to-DDR2SDRAMAddressMap

NOTE:Misnumberofcolumns(asdeterminedbyPAGESIZE)minus1,Pisnumberofbanks(asdeterminedby

IBANK)minus1,andNisnumberofrows(asdeterminedbybothPAGESIZEandIBANK)minus1.

24DDR2MemoryControllerSPRU986B–November2007

SubmitDocumentationFeedback