www.ti.com

4.6PeripheralBusBurstPriorityRegister(PBBPR)

DDR2MemoryControllerRegisters

Theperipheralbusburstpriorityregister(PBBPR)helpspreventcommandstarvationwithintheDDR2

memorycontroller.Toavoidcommandstarvation,theDDR2memorycontrollermomentarilyraisesthe

priorityoftheoldestcommandinthecommandFIFOafterasetnumberoftransfershavebeenmade.

ThePR_OLD_COUNTbitsetsthenumberoftransfersthatmustbemadebeforetheDDR2memory

controllerraisesthepriorityoftheoldestcommand.ThePBBPRisshowninFigure24anddescribedin

Table30.SeeSection2.8.2formoredetailsoncommandstarvation.

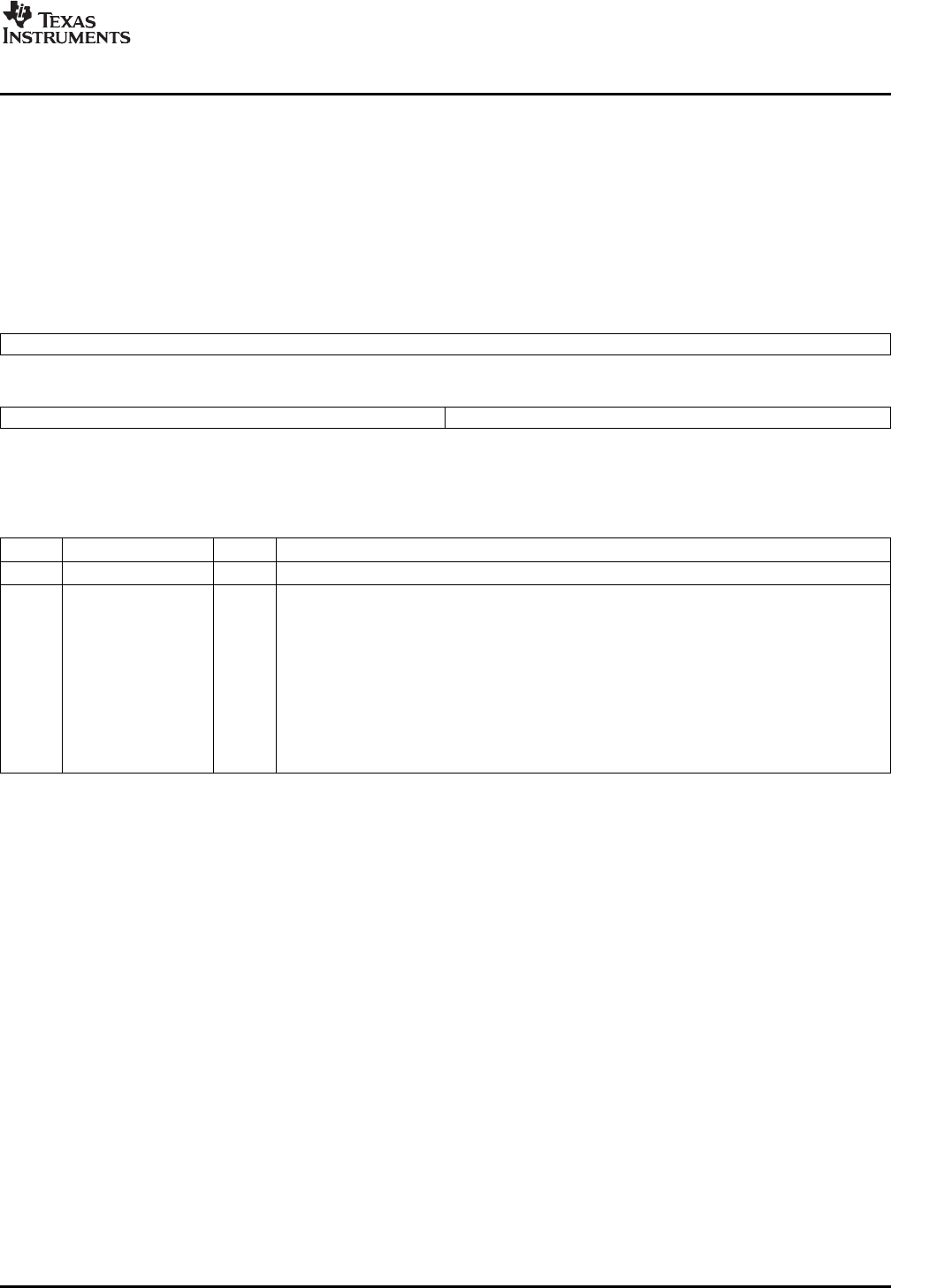

Figure24.PeripheralBusBurstPriorityRegister(PBBPR)

3116

Reserved

R-0

15870

ReservedPR_OLD_COUNT

R-0R/W-FFh

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table30.PeripheralBusBurstPriorityRegister(PBBPR)FieldDescriptions

BitFieldValueDescription

31-8Reserved0Reserved

7-0PR_OLD_COUNT0-FFhPriorityraiseoldcounter.SpecifiesthenumberofmemorytransfersafterwhichtheDDR2

memorycontrollerwillelevatethepriorityoftheoldestcommandinthecommandFIFO.Setting

thisfieldtoFFhdisablesthisfeature,therebyallowingoldcommandstostayintheFIFO

indefinitely.

01memorytransfer

12memorytransfers

23memorytransfers

3-FEh4to255memorytransfers

FFhFeaturedisabled,commandsmaystayincommandFIFOindefinitely

SPRU986B–November2007DDR2MemoryController47

SubmitDocumentationFeedback