Functional Description

13-3

Serial Peripheral Interface (SPI)

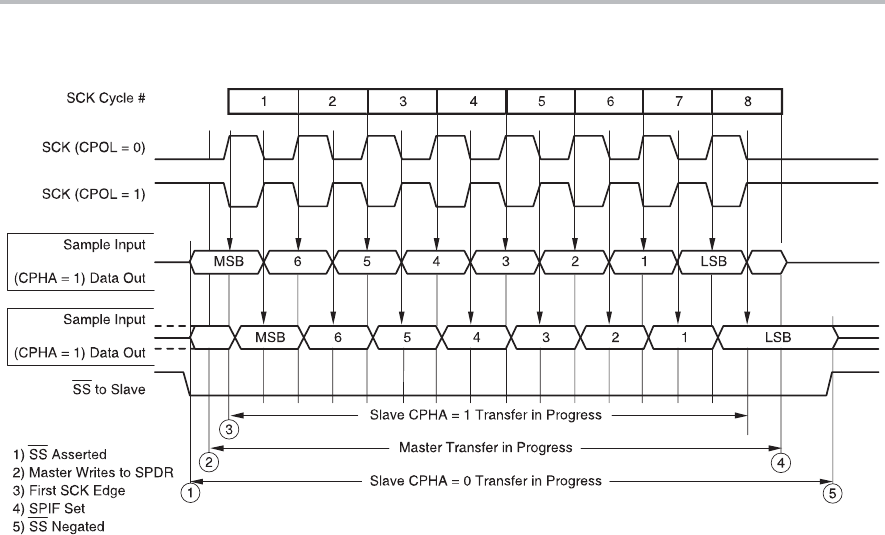

Figure 13−2. SPI Clock/Data Timing

During an SPI transfer, data is simultaneously transmitted and received. A

serial clock line synchronizes shifting and sampling of the information on the

two serial data lines.

A slave-select line allows individual selection of a slave SPI device; slave de-

vices that are not selected do not interfere with SPI bus activities. On a master

SPI device, the select line can optionally be used to indicate a multiple master

bus contention (refer to Figure 13−2).

A section of internal RAM from 80

H

to FF

H

can be used as a FIFO to extend

the buffering for receive and transmit. The size of the FIFO can range in size

from 2 to 128 bytes.