Bit Addressable SFRs (alphabetical)

F-9

Bit-Addressable SFRs (alphabetical)

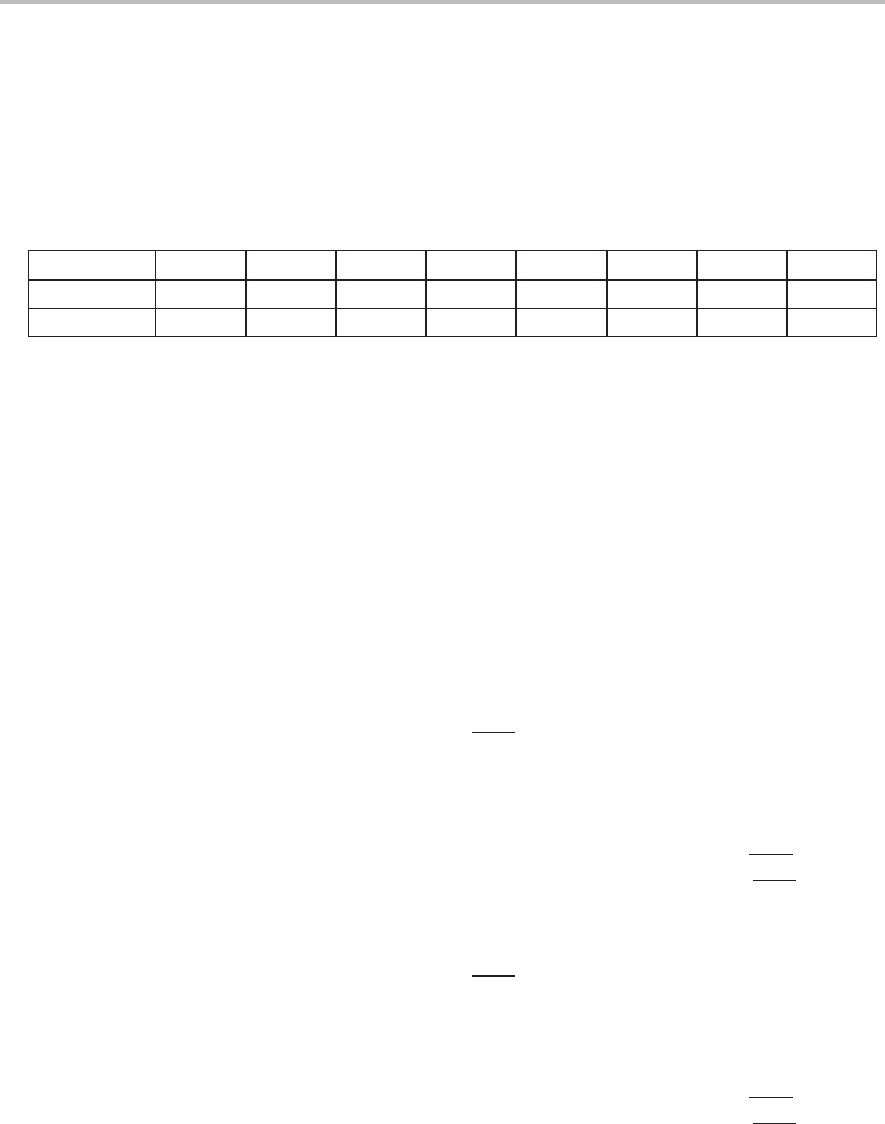

Timer Control (TCON)

SFR Name: TCON

SFR Address: 88

H

Bit−Addressable: Yes

Bit−Definitions:

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

Name TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

Bit Address 8F

H

8E

H

8D

H

8C

H

8B

H

8A

H

89

H

88

H

TF1—Timer 1 Overflow Flag. This bit is set by the MCU when Timer 1

overflows from FFFF

H

back to 0000

H

. Cleared by software, or cleared

automatically by hardware if a Timer 1 interrupt is triggered.

TR1—Timer 1 Run Control. When this bit is set, Timer 1 counts depending

on its configuration in TMOD. When this bit is clear, Timer 1 is stopped.

TF0—Timer 0 Overflow Flag. This bit is set by the MCU when Timer 0

overflows from FFFF

H

back to 0000

H

. Cleared by software, or cleared

automatically by hardware if a Timer 0 interrupt is triggered.

TR0—Timer 1 Run Control. When this bit is set, Timer 0 counts depending

on its configuration in TMOD. When this bit is clear, Timer 0 is stopped.

IE1—External 1 Interrupt Flag. This bit is set by the MCU when an external

1 interrupt is detected on the INT1 line. Cleared by software, or cleared auto-

matically by hardware if an external 1 interrupt is triggered.

IT1—External 1 Interrupt Type Flag. This bit controls whether or not external

1 interrupt is edge-triggered or low-level-triggered. If this bit is set, external 1

interrupt is triggered when a 1-0 transition is detected on the INT1

line. If this

bit is clear, external 1 interrupt is triggered continuously when INT1

is at a low

state.

IE0—External 0 Interrupt Flag. This bit is set by the MCU when an external

0 interrupt is detected on the INT0

line. Cleared by software, or cleared auto-

matically by hardware if an external 1 interrupt is triggered.

IT0—External 0 Interrupt Type Flag. This bit controls whether or not external

0 interrupt is edge-triggered or low-level-triggered. If this bit is set, external 1

interrupt is triggered when a 1-0 transition is detected on the INT0

line. If this

bit is clear, external 0 interrupt is triggered continuously when INT0

is at a low

state.