Startup Timing

7-9

System Timing

7.3 Startup Timing

When power is turned on, or a reset is initiated, a power-on delay circuit is im-

plemented with a 17-bit counter to guarantee that the power supply has

reached a certain level, and the oscillator is stable. The delay introduced by

this counter is:

24MHz System clock: (2

17

− 1) S (1/24) S 10

−6

= 0.005461s

1MHz System clock: (2

17

− 1) S 10

−6

= 0.131071s

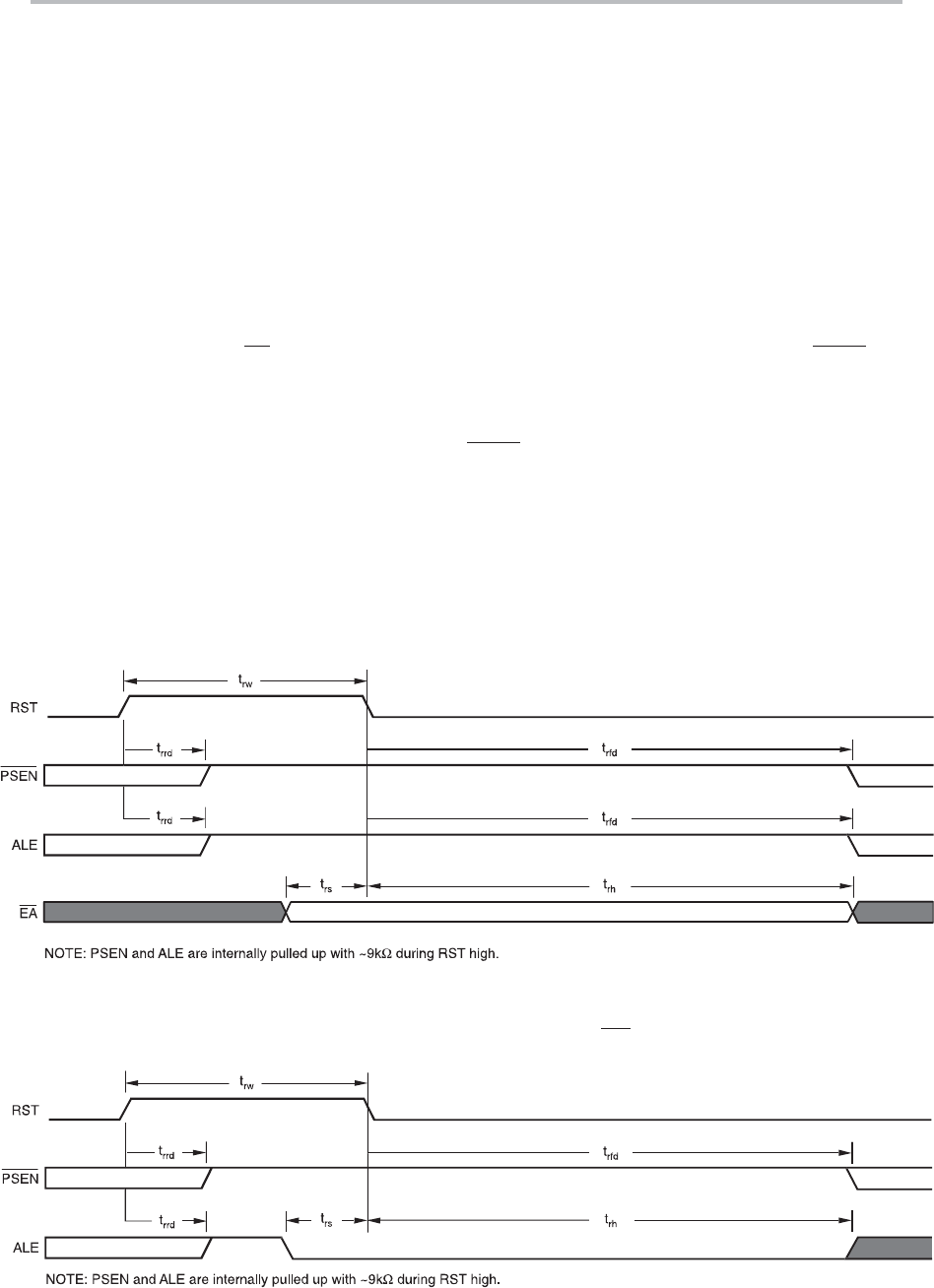

7.3.1 Normal-Mode Power-On Reset Timing

EA is sampled during power-on reset for code security purposes. PSEN and

ALE are internally pulled up during reset for serial and parallel flash program-

ming mode detection.

After the reset sequence, PSEN

and ALE signals are driven by the CPU, and

the internal pull up resistors are removed for saving power.

7.3.2 Flash Programming Mode Power-On Reset Timing

EA is ignored for serial and parallel flash programming operations.

Figure 7−5. Reset Timing

Figure 7−6. Parallel Flash Programming Power-On Timing (EA is ignored)