S1C88650 TECHNICAL MANUAL EPSON 127

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Interrupt and Standby Status)

5.14 Interrupt and Standby Status

■ Types of interrupts

4 systems and 31 types of interrupts have been

provided for the S1C88650.

External interrupt

•K00–K07 input interrupt (8 types)

Internal interrupt

•Clock timer interrupt (4 types)

•Programmable timer interrupt (16 types)

•Serial interface interrupt (3 types)

An interrupt factor flag that indicates the genera-

tion of an interrupt factor and an interrupt enable

register that sets enable/disable for interrupt

requests have been provided for each interrupt

and interrupt generation can be optionally set for

each factor.

In addition, an interrupt priority register has been

provided for each system of interrupts and the

priority of interrupt processing can be set to 3

levels in each system.

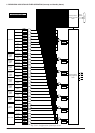

Figure 5.14.1 shows the configuration of the

interrupt circuit.

Refer to the explanations of the respective periph-

eral circuits for details on each interrupt.

■ HALT status

By executing the program's HALT instruction, the

S1C88650 enters the HALT status.

Since CPU operation stops in the HALT status,

power consumption can be reduced with only

peripheral circuit operation.

Cancellation of the HALT status is done by initial

reset or an optional interrupt request, and the CPU

restarts program execution from an exception

processing routine.

See the "S1C88 Core CPU Manual" for the HALT

status and reactivation sequence.

■ SLEEP status

By executing the program's SLP instruction, the

S1C88650 enters the SLEEP status.

Since the operation of the CPU and peripheral

circuits stop completely in the SLEEP status, power

consumption can be reduced even more than in the

HALT status.

Cancellation of the SLEEP status is done by initial

reset or an input interrupt from the input port. The

CPU reactivates after waiting 128/f

OSC1 or 512/

fOSC3 seconds of oscillation stabilization time (the

oscillation stabilization time varies depending on

the operating clock being used when the SLP

instruction is executed). At this time, the CPU

restarts program execution from an exception

processing routine (input interrupt routine).

Note: The oscillation becomes unstable for a while

after SLEEP status is cancelled, the wait

time for restarting the CPU may be longer

than 128/f

OSC1

or 512/f

OSC3

seconds.

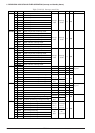

5.14.1 Interrupt generation conditions

The interrupt factor flags that indicate the genera-

tion of their respective interrupt factors are pro-

vided for the previously indicated 4 systems and 31

types of interrupts and they will be set to "1" by the

generation of a factor.

In addition, interrupt enable registers with a 1 to 1

correspondence to each of the interrupt factor flags

are provided. An interrupt is enabled when "1" is

written and interrupt is disabled when "0" is

written.

The CPU manages the enable/disable of interrupt

requests at the interrupt priority level. An interrupt

priority register that sets the priority level is

provided for each of the interrupts of the 4 systems

and the CPU accepts only interrupts above the level

that has been indicated with the interrupt flags (I0

and I1).

Consequently, the following three conditions are

necessary for the CPU to accept the interrupt.

(1) The interrupt factor flag has been set to "1" by

generation of an interrupt factor.

(2) The interrupt enable register corresponding to

the above has been set to "1".

(3) The interrupt priority register corresponding to

the above has been set to a priority level higher

than the interrupt flag (I0 and I1) setting.

The CPU initially samples the interrupt for the first

op-code fetch cycle of each instruction. Thereupon,

the CPU shifts to the exception processing when the

above mentioned conditions have been established.

See the "S1C88 Core CPU Manual" for the exception

processing sequence.