S1C88650 TECHNICAL MANUAL EPSON 77

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Serial Interface)

SCS0, SCS1: 00FF48H•D3, D4

Select the clock source according to Table 5.8.9.3.

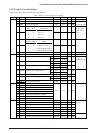

Table 5.8.9.3 Clock source selection

SCS1

1

1

0

0

SCS0

1

0

1

0

Clock source

Programmable timer

f

OSC3 / 4

fOSC3 / 8

f

OSC3 / 16

SCS0 and SCS1 can also be read out.

In the clock synchronous slave mode, setting of this

register is invalid.

At initial reset, this register is set to "0" (fOSC3/16).

SDP: 00FF4BH•D0

Selects the serial data input/output permutation.

When "1" is written: MSB first

When "0" is written: LSB first

Reading: Valid

Select whether the data input/output permutation

will be MSB first or LSB first.

At initial reset, SDP is set to "0" (LSB first).

STPB: 00FF4BH•D1

Selects the stop bit length for asynchronous data

transfer.

When "1" is written: 2 bits

When "0" is written: 1 bit

Reading: Valid

STPB is the stop bit select register that is effective in

asynchronous mode. When "1" is written to STPB,

the stop bit length is set to 2 bits, and when "0" is

written, it is set to 1 bit.

In clock synchronous mode, no start/stop bits can

be added to transfer data. Therefore, setting STPB

becomes invalid.

At initial reset, STPB is set to "0" (1 bit).

EPR: 00FF48H•D6

Selects the parity function.

When "1" is written: With parity

When "0" is written: Non parity

Reading: Valid

Selects whether or not to check parity of the

received data and to add a parity bit to the trans-

mitting data. When "1" is written to EPR, the most

significant bit of the received data is considered to

be the parity bit and a parity check is executed. A

parity bit is added to the transmitting data. When

"0" is written, neither checking is done nor is a

parity bit added.

Parity is valid only in asynchronous mode and the

EPR setting becomes invalid in the clock synchro-

nous mode.

At initial reset, EPR is set to "0" (non parity).

PMD: 00FF48H•D5

Selects odd parity/even parity.

When "1" is written: Odd parity

When "0" is written: Even parity

Reading: Valid

When "1" is written to PMD, odd parity is selected

and even parity is selected when "0" is written. The

parity check and addition of a parity bit is only

valid when "1" has been written to EPR. When "0"

has been written to EPR, the parity setting by PMD

becomes invalid.

At initial reset, PMD is set to "0" (even parity).

TXEN: 00FF49H•D0

Sets the serial interface to the transmitting enable

status.

When "1" is written: Transmitting enable

When "0" is written: Transmitting disable

Reading: Valid

When "1" is written to TXEN, the serial interface

shifts to the transmitting enable status and shifts to

the transmitting disable status when "0" is written.

Set TXEN to "0" when making the initial settings of

the serial interface and similar operations.

At initial reset, TXEN is set to "0" (transmitting

disable).

TXTRG: 00FF49H•D1

Functions as the transmitting start trigger and the

operation status indicator (transmitting/stop

status).

When "1" is read: During transmitting

When "0" is read: During stop

When "1" is written: Transmitting start

When "0" is written: Invalid

Starts the transmitting when "1" is written to

TXTRG after writing the transmitting data.

TXTRG can be read as the status. When set to "1", it

indicates transmitting operation, and "0" indicates

transmitting stop.

At initial reset, TXTRG is set to "0" (during stop).

RXEN: 00FF49H•D2

Sets the serial interface to the receiving enable status.

When "1" is written: Receiving enable

When "0" is written: Receiving disable

Reading: Valid

When "1" is written to RXEN, the serial interface

shifts to the receiving enable status and shifts to the

receiving disable status when "0" is written.

Set RXEN to "0" when making the initial settings of

the serial interface and similar operations.

At initial reset, RXEN is set to "0" (receiving disable).