130 EPSON S1C88650 TECHNICAL MANUAL

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Interrupt and Standby Status)

5.14.3 Interrupt enable register

The interrupt enable register has a 1 to 1 corre-

spondence with each interrupt factor flag and

enable/disable of interrupt requests can be set.

When "1" is written to the interrupt enable register,

an interrupt request is enabled, and is disabled

when "0" is written.

This register also permits reading, thus making it

possible to confirm that a status has been set.

At initial reset, the interrupt enable registers are set

to "0" and shifts to the interrupt disable status.

Table 5.14.3.1 shows the correspondence between

the interrupt enable registers and the interrupt

factor flags.

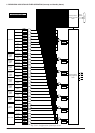

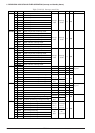

Table 5.14.3.1 Interrupt enable registers and interrupt factor flags

Interrupt

K07 input

K06 input

K05 input

K04 input

K03 input

K02 input

K01 input

K00 input

Timer 0 underflow

Timer 0 compare match

Timer 1 underflow

Timer 1 compare match

Timer 2 underflow

Timer 2 compare match

Timer 3 underflow

Timer 3 compare match

Timer 4 underflow

Timer 4 compare match

Timer 5 underflow

Timer 5 compare match

Timer 6 underflow

Timer 6 compare match

Timer 7 underflow

Timer 7 compare match

Serial interface receiving error

Serial interface receiving completion

Serial interface transmitting completion

Clock timer 32 Hz

Clock timer 8 Hz

Clock timer 2 Hz

Clock timer 1 Hz

Interrupt enable register

FK07

FK06

FK05

FK04

FK03

FK02

FK01

FK00

FTU0

FTC0

FTU1

FTC1

FTU2

FTC2

FTU3

FTC3

FTU4

FTC4

FTU5

FTC5

FTU6

FTC6

FTU7

FTC7

FSERR

FSREC

FSTRA

FTM32

FTM8

FTM2

FTM1

00FF28H·D7

00FF28H·D6

00FF28H·D5

00FF28H·D4

00FF28H·D3

00FF28H·D2

00FF28H·D1

00FF28H·D0

00FF29H·D0

00FF29H·D1

00FF29H·D2

00FF29H·D3

00FF29H·D4

00FF29H·D5

00FF29H·D6

00FF29H·D7

00FF2EH·D0

00FF2EH·D1

00FF2EH·D2

00FF2EH·D3

00FF2EH·D4

00FF2EH·D5

00FF2EH·D6

00FF2EH·D7

00FF27H·D2

00FF27H·D1

00FF27H·D0

00FF26H·D3

00FF26H·D2

00FF26H·D1

00FF26H·D0

Interrupt factor flag

EK07

EK06

EK05

EK04

EK03

EK02

EK01

EK00

ETU0

ETC0

ETU1

ETC1

ETU2

ETC2

ETU3

ETC3

ETU4

ETC4

ETU5

ETC5

ETU6

ETC6

ETU7

ETC7

ESERR

ESREC

ESTRA

ETM32

ETM8

ETM2

ETM1

00FF24H·D7

00FF24H·D6

00FF24H·D5

00FF24H·D4

00FF24H·D3

00FF24H·D2

00FF24H·D1

00FF24H·D0

00FF25H·D0

00FF25H·D1

00FF25H·D2

00FF25H·D3

00FF25H·D4

00FF25H·D5

00FF25H·D6

00FF25H·D7

00FF2CH·D0

00FF2CH·D1

00FF2CH·D2

00FF2CH·D3

00FF2CH·D4

00FF2CH·D5

00FF2CH·D6

00FF2CH·D7

00FF23H·D2

00FF23H·D1

00FF23H·D0

00FF22H·D3

00FF22H·D2

00FF22H·D1

00FF22H·D0