S1C88650 TECHNICAL MANUAL EPSON 63

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Serial Interface)

This register setting is invalid in clock synchronous

slave mode and the external clock input from the

_________

SCLK terminal is used.

When the "programmable timer" is selected, the

programmable timer 1 underflow signal is divided

by 2 and this signal is used as the clock source.

With respect to the transfer rate setting, see "5.10

Programmable Timer".

At initial reset, the synchronous clock is set to

"f

OSC3

/16".

Whichever clock is selected, the signal is further

divided by 16 and then used as the synchronous

clock.

Furthermore, external clock input is used as is for

_________

SCLK in clock synchronous slave mode.

Table 5.8.4.2 shows an examples of transfer rates and

OSC3 oscillation frequencies when the clock source

is set to programmable timer.

When the demultiplied signal of the OSC3 oscilla-

tion circuit is made the clock source, it is necessary

to turn the OSC3 oscillation ON, prior to using the

serial interface.

A time interval of several msec to several 10 msec,

from the turning ON of the OSC3 oscillation circuit

to until the oscillation stabilizes, is necessary, due to

the oscillation element that is used. Consequently,

you should allow an adequate waiting time after

turning ON of the OSC3 oscillation, before starting

transmitting/receiving of serial interface. (The

oscillation start time will vary somewhat depending

on the oscillator and on the externally attached parts.

Refer to the oscillation start time example indicated

in Chapter 8, "ELECTRICAL CHARACTERISTICS".)

At initial reset, the OSC3 oscillation circuit is set to

ON status.

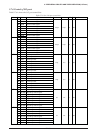

Transfer rate

(bps)

19,200

9,600

4,800

2,400

1,200

600

300

150

PST1X

00H

00H

00H

00H

00H

00H

02H

02H

RDR1X

03H

07H

0FH

1FH

3FH

7FH

1FH

3FH

PST1X

00H

00H

00H

00H

00H

00H

03H

03H

RDR1X

04H

09H

13H

27H

4FH

9FH

09H

13H

PST1X

00H

00H

00H

00H

00H

00H

01H

02H

RDR1X

05H

0BH

17H

2FH

5FH

BFH

BFH

5FH

f

OSC3

= 2.4756 MHz f

OSC3

= 3.0720 MHz f

OSC3

= 3.6864 MHz

OSC3 oscillation frequency / Programmable timer settings

Table 5.8.4.2 OSC3 oscillation frequencies and transfer rates

Data input

Data output

CLOCK output

READY input

SIN(P10)

SOUT(P11)

SCLK(P12)

SRDY(P13)

External

serial device

S1C88650

Data input

Data output

CLOCK input

READY output

SIN(P10)

SOUT(P11)

SCLK(P12)

Input port(Kxx)

External

serial device

S1C88650

(a) Clock synchronous master mode

(b) Clock synchronous slave mode

(c) Asynchronous 7-bit/8-bit mode

Fig. 5.8.3.1 Connection examples of serial interface I/O terminals

5.8.4 Clock source

There are four clock sources and selection is made

by setting the two bits of the clock source selection

register SCS0 and SCS1 as shown in table below.

Table 5.8.4.1 Clock source

SCS1

1

1

0

0

SCS0

1

0

1

0

Clock source

Programmable timer

f

OSC3 / 4

fOSC3 / 8

f

OSC3 / 16

Data input

Data output

SIN(P10)

SOUT(P11)

External

serial device

S1C88650

f

OSC3

1/4

1/8

1/16

1/16

Synchro-

nous clock

Programmable timer 1

underflow signal

SCLK

(Clock synchronous slave mode)

Divider Selector Selector

1/2

OSC3

oscillation

circuit

Fig. 5.8.4.1

Division of the synchronous clock

∗ Since the underflow signal only is used as the clock source, the

CDR1X register value does not affect the transfer rates.