S1C88650 TECHNICAL MANUAL EPSON 49

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Input Ports)

KCP00–KCP07: 00FF52H

Sets the interrupt generation condition (interrupt

generation timing) for input port terminals K00–

K07.

When "1" is written: Falling edge

When "0" is written: Rising edge

Reading: Valid

KCP0x is the input comparison register which

corresponds to the input port K0x. Interrupt in

those ports which have been set to "1" is generated

on the falling edge of the input and in those set to

"0" on the rising edge.

At initial reset, this register is set to "1" (falling

edge).

CTK00L–CTK02L: 00FF58H•D0–D2

Sets the input level check time of the chattering-

eliminate circuit for the K00–K03 input port

interrupts as shown in Table 5.5.5.2.

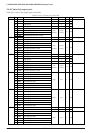

Table 5.5.5.2 Setting the input level check time

CTK02L

1

1

1

1

0

0

0

0

CTK01L

1

1

0

0

1

1

0

0

CTK00L

1

0

1

0

1

0

1

0

Input level check time [sec]

4/f

OSC3

2/f

OSC3

1/f

OSC3

4096/f

OSC1

2048/f

OSC1

512/f

OSC1

128/f

OSC1

None

Be sure to disable interrupts before changing the

contents of this register. Unnecessary interrupts

may occur if the register is changed when the

corresponding input port interrupts have been

enabled by the interrupt enable register EK0x.

At initial reset, this register is set to "0" (None).

CTK00H–CTK02H: 00FF58H•D4–D6

Sets the input level check time of the chattering-

eliminate circuit for the K04–K07 input port

interrupts as shown in Table 5.5.5.3.

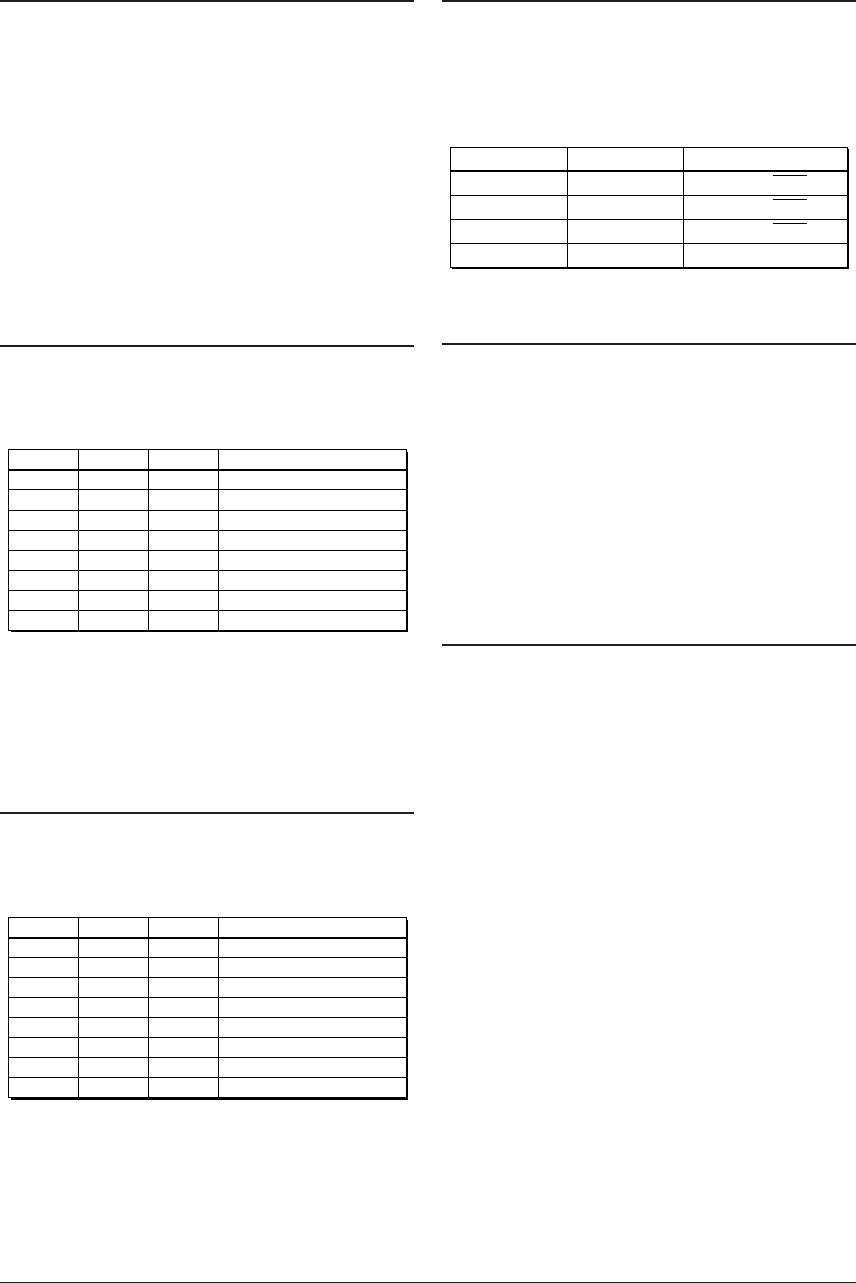

Table 5.5.5.3 Setting the input level check time

CTK02H

1

1

1

1

0

0

0

0

CTK01H

1

1

0

0

1

1

0

0

CTK00H

1

0

1

0

1

0

1

0

Input level check time [sec]

4/f

OSC3

2/f

OSC3

1/f

OSC3

4096/f

OSC1

2048/f

OSC1

512/f

OSC1

128/f

OSC1

None

Be sure to disable interrupts before changing the

contents of this register. Unnecessary interrupt may

occur if the register is changed when the

corresponding input port interrupts have been

enabled by the interrupt enable register EK0x.

At initial reset, this register is set to "0" (None).

PK00, PK01: 00FF20H•D6, D7

Sets the input interrupt priority level. PK00 and

PK01 are the interrupt priority registers

corresponding to the input interrupts.

Table 5.5.5.4 shows the interrupt priority level

which can be set by this register.

Table 5.5.5.4 Interrupt priority level settings

PK01 PK00 Interrupt priority level

1

1

0

0

1

0

1

0

Level 3 (IRQ3)

Level 2 (IRQ2)

Level 1 (IRQ1)

Level 0 (None)

At initial reset, this register is set to "0" (level 0).

EK00–EK07: 00FF24H

How interrupt generation to the CPU is permitted

or prohibited.

When "1" is written: Interrupt permitted

When "0" is written: Interrupt prohibited

Reading: Valid

EK0x is the interrupt enable register which

correspond to the input port K0x.

Interrupt is permitted in those terminals set to "1"

and prohibited in those set to "0".

At initial reset, this register is set to "0" (interrupt

prohibited).

FK00–FK07: 00FF28H

Indicates the generation state for an input interrupt.

When "1" is read: Interrupt factor present

When "0" is read:

Interrupt factor not present

When "1" is written: Reset factor flag

When "0" is written: Invalid

The interrupt factor flag FK0x corresponds to K0x is

set to "1" by the occurrence of an interrupt

generation condition.

When set in this manner, if the corresponding

interrupt enable register is set to "1" and the

corresponding interrupt priority register is set to a

higher level than the setting of interrupt flags (I0

and I1), an interrupt will be generated to the CPU.

Regardless of the interrupt enable register and

interrupt priority register settings, the interrupt

factor flag will be set to "1" by the occurrence of an

interrupt generation condition.

To accept the subsequent interrupt after interrupt

generation, re-setting of the interrupt flags (set

interrupt flag to lower level than the level indicated

by the interrupt priority registers, or execute the

RETE instruction) and interrupt factor flag reset are

necessary. The interrupt factor flag is reset to "0" by

writing "1".

At initial reset, this flag is all reset to "0".