146 EPSON S1C88650 TECHNICAL MANUAL

8 ELECTRICAL CHARACTERISTICS

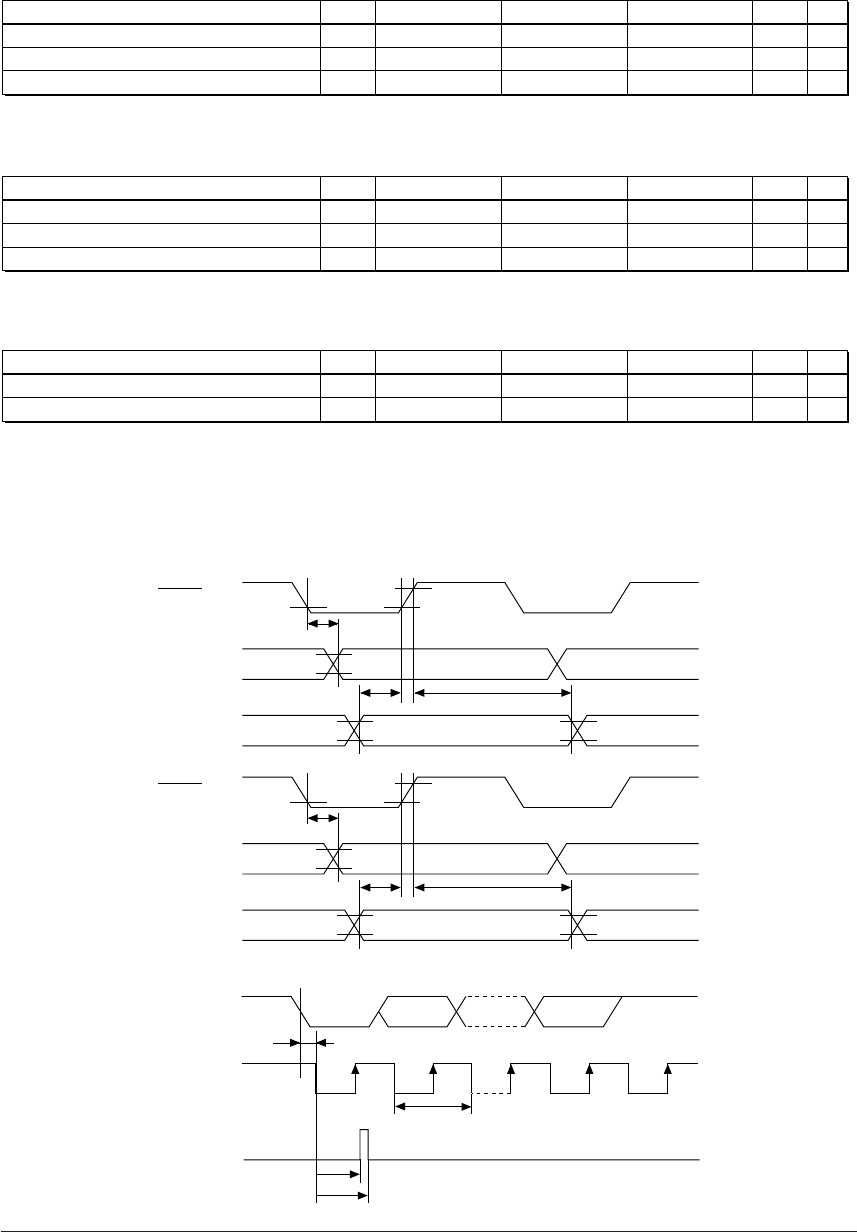

■ Serial interface

• Clock synchronous master mode

Item

Symbol

Min. Typ. Max. Unit

Transmitting data output delay time

Receiving data input set-up time

Receiving data input hold time

t

smd

t

sms

t

smh

ns

ns

ns

Note

250

100

100

Condition: V

DD

= 1.8 to 3.6 V, V

SS

= 0 V, Ta = 25°C, V

IH1

= 0.8V

DD

, V

IL1

= 0.2V

DD

, V

OH

= 0.8V

DD

, V

OL

= 0.2V

DD

• Clock synchronous slave mode

Item

Symbol

Min. Typ. Max. Unit

Transmitting data output delay time

Receiving data input set-up time

Receiving data input hold time

t

ssd

t

sss

t

ssh

ns

ns

ns

Note

100

100

250

Condition: V

DD

= 1.8 to 3.6 V, V

SS

= 0 V, Ta = 25°C, V

IH1

= 0.8V

DD

, V

IL1

= 0.2V

DD

, V

OH

= 0.8V

DD

, V

OL

= 0.2V

DD

• Asynchronous system

Min. Typ. Max.

t

sa

1

t

sa

2

s

s

1

2

Note) 1

2

Start bit detection error time is a logical delay time from inputting the start bit until internal sampling begins operating.

(Time as far as AC is excluded.)

Erroneous start bit detection range time is a logical range to detect whether a LOW level (start bit) has been input again

after a start bit has been detected and the internal sampling clock has started.

When a HIGH level is detected, the start bit detection circuit is reset and goes into a wait status until the next start bit.

(Time as far as AC is excluded.)

0

9

t

/16

t

/16

10

t

/16

Item

Symbol

Unit

Start bit detection error time

Erroneous start bit detection range time

Note

Condition: V

DD

= 1.8 to 3.6 V, V

SS

= 0 V, Ta = 25°C

SCLK OUT

SOUT

SIN

VOH

VOH

VOL

tsms tsmh

tsmd

VIH1

VIL1

VOL

SCLK IN

SOUT

SIN

VIH1

VOH

VOL

tsss tssh

tssd

VIH1

VIL1

VIL1

t

sa

1

t

t

sa

2

SIN

Start bit

Sampling

clock

Erroneous

start bit

detection signal

Stop bit