S1C88650 TECHNICAL MANUAL EPSON 9

3 CPU AND BUS CONFIGURATION

When multiple exception processing factors are

generated at the same time, execution starts with

the highest priority item.

The priority sequence shown in Table 3.3.1 assumes

that the interrupt priority levels are all the same.

The interrupt priority levels can be set by software

in each system. (See Section 5.14, "Interrupt and

Standby Status".)

Note: For exception processing other than reset,

SC (system condition flag) and PC (program

counter) are evacuated to the stack and

branches to the exception processing

routines. Consequently, when returning to

the main routine from exception processing

routines, please use the RETE instruction.

See the "S1C88 Core CPU Manual" for information

on CPU operations when an exception processing

factor is generated.

3.4 CC (Customized Condition Flag)

The S1C88650 does not use the customized condi-

tion flag (CC) in the core CPU. Accordingly, it

cannot be used as a branching condition for the

conditional branching instruction (JRS, CARS).

3.5 Chip Mode

3.5.1 MCU mode and MPU mode

The chip operating mode can be set to one of two

_______

settings using the MCU/MPU terminal.

■

_______

MCU mode...Set the MCU/MPU terminal to HIGH

Switch to this setting when using internal ROM.

With respect to areas other than internal

memory, external memory can even be

expanded. See Section 3.5.2, "Bus mode", for the

memory map.

In the MCU mode, during initial reset, only

systems in internal memory are activated.

Internal program ROM is normally fixed as the

top portion of the program memory from the

common area (logical space 0000H–7FFFH).

Exception processing vectors are assigned in

internal program ROM. Furthermore, the

application initialization routines that start with

reset exception processing must likewise be

written to internal program ROM. Since bus and

other settings which correlate with external

expanded memory can be executed in software,

this processing is executed in the initialization

routine written to internal program ROM. Once

these bus mode settings are made, external

memory can be accessed.

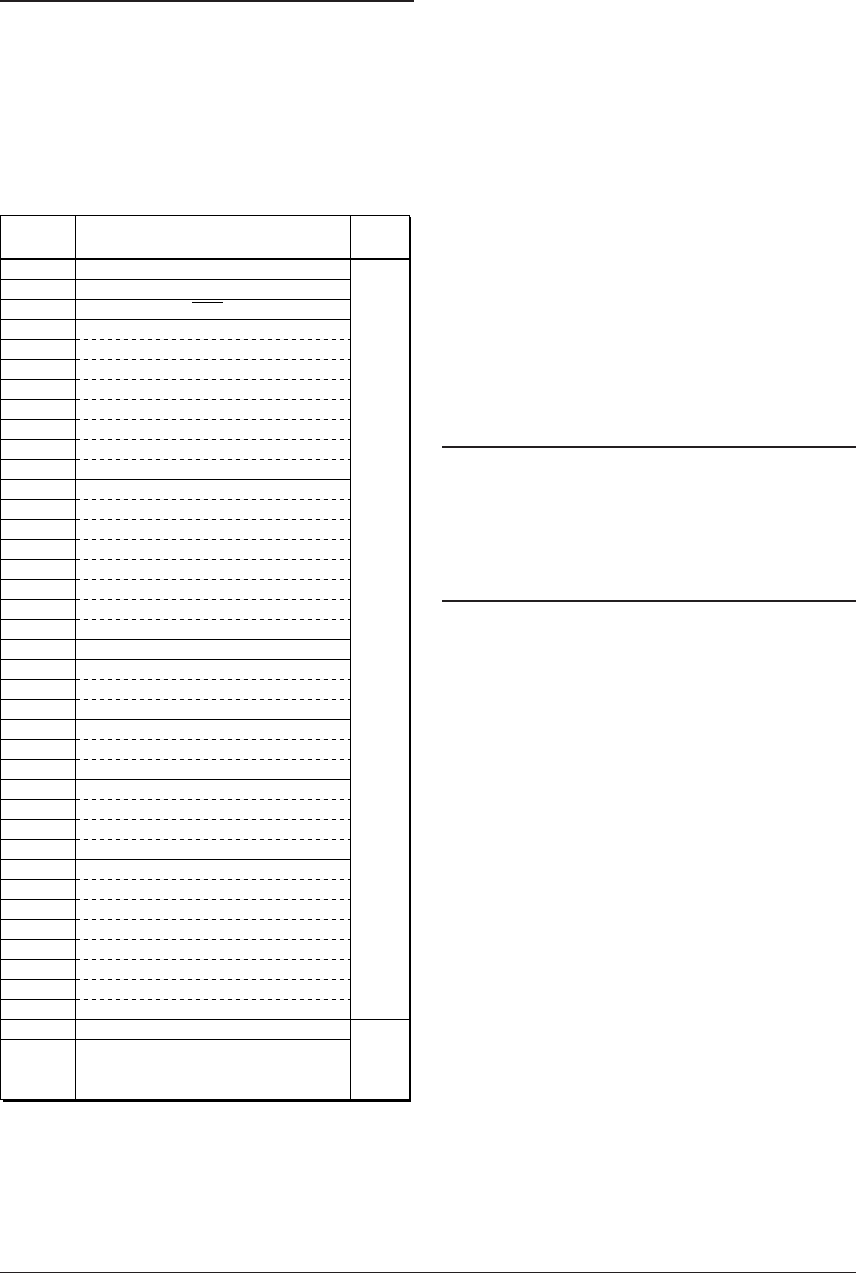

3.3 Exception Processing Vectors

000000H–00004BH in the program area of the

S1C88650 is assigned as exception processing

vectors. Furthermore, from 00004EH to 0000FFH,

software interrupt vectors are assignable to any two

bytes which begin with an even address.

Table 3.3.1 lists the vector addresses and the

exception processing factors to which they corre-

spond.

Table 3.3.1 Exception processing vector table

Vector

address

000000H

000002H

000004H

000006H

000008H

00000AH

00000CH

00000EH

000010H

000012H

000014H

000016H

000018H

00001AH

00001CH

00001EH

000020H

000022H

000024H

000026H

000028H

00002AH

00002CH

00002EH

000030H

000032H

000034H

000036H

000038H

00003AH

00003CH

00003EH

000040H

000042H

000044H

000046H

000048H

00004AH

00004CH

00004EH

:

0000FEH

Priority

High

↑

↓

Low

No

priority

rating

Exception processing factor

Reset

Zero division

Watchdog timer (NMI)

K07 input interrupt

K06 input interrupt

K05 input interrupt

K04 input interrupt

K03 input interrupt

K02 input interrupt

K01 input interrupt

K00 input interrupt

PTM 0 underflow interrupt

PTM 0 compare match interrupt

PTM 1 underflow interrupt

PTM 1 compare match interrupt

PTM 2 underflow interrupt

PTM 2 compare match interrupt

PTM 3 underflow interrupt

PTM 3 compare match interrupt

System reserved (cannot be used)

Serial I/F error interrupt

Serial I/F receiving complete interrupt

Serial I/F transmitting complete interrupt

System reserved (cannot be used)

System reserved (cannot be used)

System reserved (cannot be used)

Clock timer 32 Hz interrupt

Clock timer 8 Hz interrupt

Clock timer 2 Hz interrupt

Clock timer 1 Hz interrupt

PTM 4 underflow interrupt

PTM 4 compare match interrupt

PTM 5 underflow interrupt

PTM 5 compare match interrupt

PTM 6 underflow interrupt

PTM 6 compare match interrupt

PTM 7 underflow interrupt

PTM 7 compare match interrupt

System reserved (cannot be used)

Software interrupt

For each vector address and the address after it, the

start address of the exception processing routine is

written into the subordinate and super ordinate

sequence. When an exception processing factor is

generated, the exception processing routine is

executed starting from the recorded address.