S1C88650 TECHNICAL MANUAL EPSON 137

6 SUMMARY OF NOTES

6.2 Precautions on Mounting

<Oscillation Circuit>

● Oscillation characteristics change depending on

conditions (board pattern, components used,

etc.).

In particular, when a ceramic or crystal

oscillator is used, use the oscillator

manufacturer's recommended values for

constants such as capacitance and resistance.

● Disturbances of the oscillation clock due to

noise may cause a malfunction. Consider the

following points to prevent this:

(1) Components which are connected to the

OSC1, OSC2, OSC3 and OSC4 terminals,

such as oscillators, resistors and capacitors,

should be connected in the shortest line.

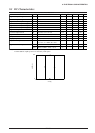

(2) As shown in the right hand figure, make a

V

SS pattern as large as possible at circum-

scription of the OSC1, OSC2, OSC3 and

OSC4 terminals and the components

connected to these terminals.

Furthermore, do not use this VSS pattern for

any purpose other than the oscillation

system.

OSC4

OSC3

V

SS

Sample VSS pattern (OSC3)

● In order to prevent unstable operation of the

oscillation circuit due to current leak between

OSC1/OSC3 and VDD, please keep enough

distance between OSC1/OSC3 and VDD or other

signals on the board pattern.

<Reset Circuit>

● The power-on reset signal which is input to the

RESET terminal changes depending on

conditions (power rise time, components used,

board pattern, etc.).

Decide the time constant of the capacitor and

resistor after enough tests have been completed

with the application product.

When the built-in pull-up resistor of the RESET

terminal is used, take into consideration

dispersion of the resistance for setting the

constant.

● In order to prevent any occurrences of unneces-

sary resetting caused by noise during operating,

components such as capacitors and resistors

should be connected to the RESET terminal in

the shortest line.

<Power Supply Circuit>

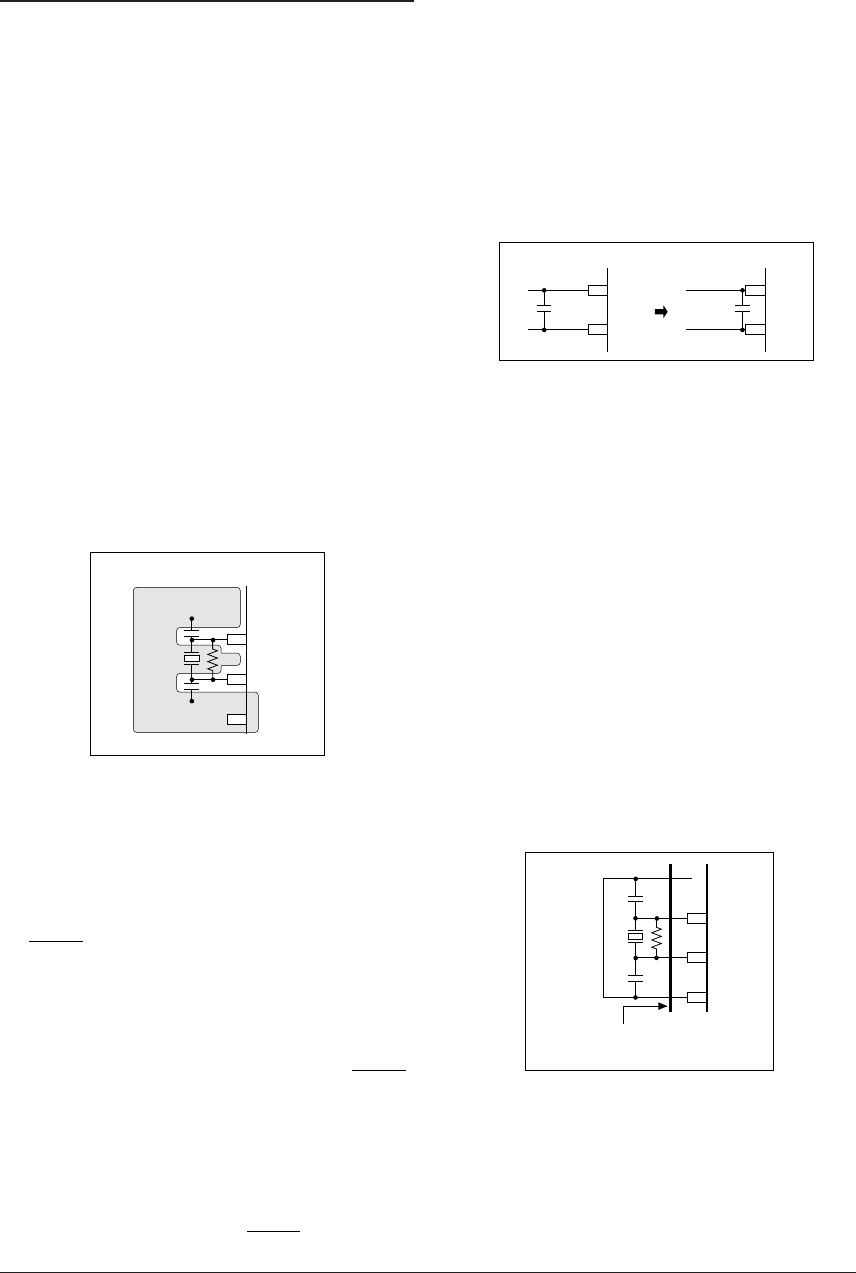

● Sudden power supply variation due to noise

may cause malfunction. Consider the following

points to prevent this:

(1) The power supply should be connected to

the VDD and VSS terminal with patterns as

short and large as possible.

(2) When connecting between the VDD and VSS

terminals with a bypass capacitor, the

terminals should be connected as short as

possible.

V

DD

V

SS

Bypass capacitor connection example

V

DD

V

SS

(3) Components which are connected to the

VD1, VC1, VC2, VC3, VC4 and VC5 terminals,

such as capacitors and resistors, should be

connected in the shortest line.

In particular, the VC1, VC2, VC3, VC4 and VC5

voltages affect the display quality.

<Arrangement of Signal Lines>

● In order to prevent generation of

electromagnetic induction noise caused by

mutual inductance, do not arrange a large

current signal line near the circuits that are

sensitive to noise such as the oscillation unit.

● When a signal line is parallel with a high-speed

line in long distance or intersects a high-speed

line, noise may generated by mutual

interference between the signals and it may

cause a malfunction.

Do not arrange a high-speed signal line

especially near circuits that are sensitive to

noise such as the oscillation unit.

OSC4

OSC3

V

SS

Large current signal line

High-speed signal line

Prohibited pattern