10 EPSON S1C88650 TECHNICAL MANUAL

3 CPU AND BUS CONFIGURATION

3.5.2 Bus mode

In order to set bus specifications to match the

configuration of external expanded memory, two

different bus modes described below are selectable

in software.

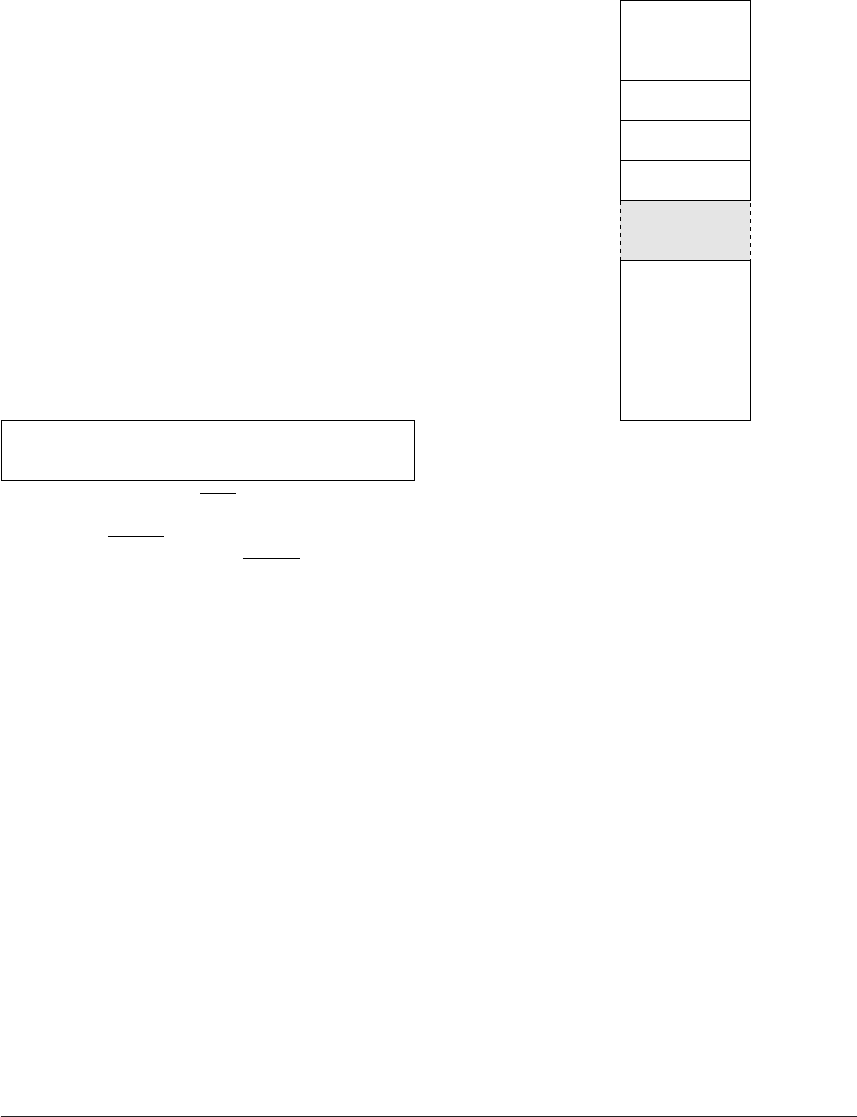

■ Single chip mode

0EFFFFH

010000H

00FFFFH

00FF00H

00FD7FH

00F800H

00F7FFH

00D800H

00D7FFH

:

00C000H

00BFFFH

000000H

- MCU mode -

Kanji font ROM

(896K bytes)

I/O memory

Display memory

Internal RAM

Unused area

Internal ROM

Fig. 3.5.2.1 Memory map for the single chip mode

The single chip mode setting applies when the

S1C88650 is used as a single chip microcom-

puter without external expanded memory.

Since this mode employs internal ROM, the

system can only be operated in the MCU mode

discussed in Section 3.5.1.

In the MPU mode, the system cannot be set to

the single chip mode.

Since there is no need for an external bus line in

this mode, terminals normally set for bus use

can be used as general purpose output ports or

I/O ports.

■ Expansion mode

The expansion mode setting applies when the

S1C88650 is used with less than 1M bytes × 3 of

external expanded memory. This mode is

usable regardless of the MCU/MPU mode

setting.

Because internal ROM is being used in the MCU

mode, external memory in this model can be

assigned to the area from 100000H to 3FFFFFH.

Since the internal ROM area is released in the

MPU mode, external memory in this model can

be assigned to the area from 000000H to

2FFFFFH.

However, the area from 00C000H to 00FFFFH is

assigned to internal memory and cannot be

used to access an external device.

When accessing internal memory in this mode,

____ ____ _____

the chip enable (CE) and read (RD)/write (WR)

signals are not output to external memory, and

the data bus (D0–D7) goes into high impedance

status (or pull-up status).

Consequently, in cases where addresses overlap

in external and internal memory, the areas in

external memory will be unavailable.

■

_______

MPU mode...Set the MCU/MPU terminal to LOW

Internal ROM area is released to an external

device source. Internal ROM then becomes

unusable and when this area is accessed, chip

____ ____ _____

enable (CE) and read (RD)/write (WR) signals

are output to external memory and the data bus

(D0–D7) become active. These signals are not

output to an external source when other areas of

internal memory are accessed.

In the MPU mode, the system is activated by

external memory.

When employing this mode, the exception

processing vectors and initialization routine

must be assigned within the common area

(000000H–007FFFH).

You can select whether to use the built-in pull-up

_______

resistor of the MCU/MPU terminal by the mask

option.

Iput port pull-up resistor

_______

MCU/MPU ..... ■■ With resistor ■■ Gate direct

Notes: •

Setting of MCU/MPU terminal is latched at

the rising edge of a reset signal input from

the RESET terminal. Therefore, if the setting

is to be changed, the RESET terminal must

be set to LOW level once again.

•

The data bus while the CPU accesses to the

internal memory can be select into high-

impedance status or pulled up to high using

the pull-up control register and mask option.

See Section 5.7, "I/O Ports (P ports)", for

details.