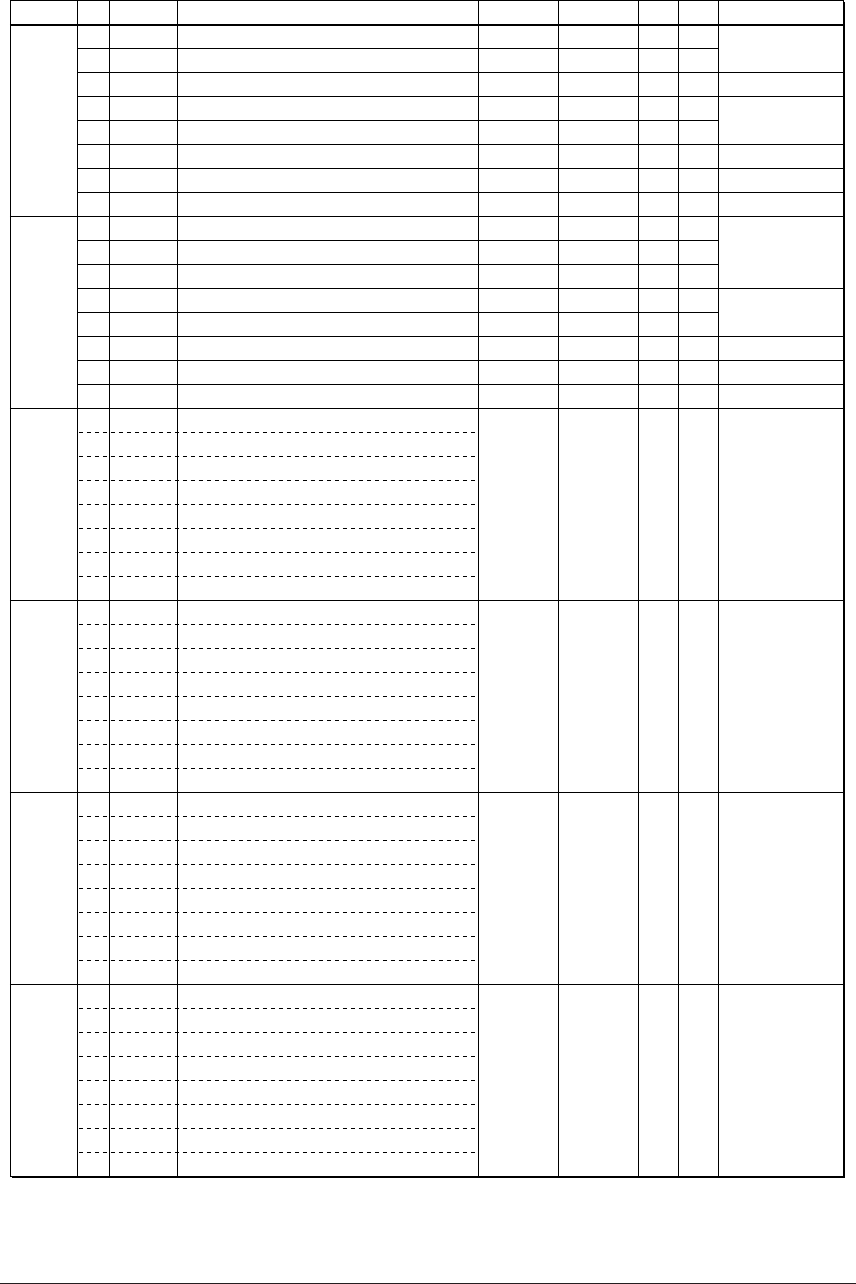

S1C88650 TECHNICAL MANUAL EPSON 31

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (I/O Memory Map)

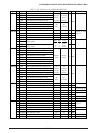

Table 5.1.1(n) I/O Memory map (00FFB0H–00FFB5H)

SR R/WAddress Bit Name Function Comment10

D7

D6

D5

D4

D3

D2

D1

D0

00FFB0

MODE16_C

PTNREN_C

–

–

–

PTRUN4

PSET4

CKSEL4

"0" when being read

Reserved register

"0" when being read

0

0

–

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

W

R/W

PTM4–5 8/16-bit mode selection

External clock 2 noise rejecter selection

–

R/W register

R/W register

PTM4 Run/Stop control

PTM4 preset

PTM4 input clock selection

16

-

bit x 1

Enable

–

1

1

Run

Preset

External clock

8

-

bit x 2

Disable

–

0

0

Stop

No operation

Internal clock

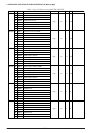

00FFB1 D7

D6

D5

D4

D3

D2

D1

D0

–

–

–

–

–

PTRUN5

PSET5

CKSEL5

–

–

–

R/W register

R/W register

PTM5 Run/Stop control

PTM5 preset

PTM5 input clock selection

Constantly "0" when

being read

Reserved register

"0" when being read

–

–

–

0

0

0

0

0

R/W

R/W

R/W

W

R/W

–

–

–

0

0

Stop

No operation

Internal clock

–

–

–

1

1

Run

Preset

External clock

D7

D6

D5

D4

D3

D2

D1

D0

RDR47

RDR46

RDR45

RDR44

RDR43

RDR42

RDR41

RDR40

PTM4 reload data D7 (MSB)

PTM4 reload data D6

PTM4 reload data D5

PTM4 reload data D4

PTM4 reload data D3

PTM4 reload data D2

PTM4 reload data D1

PTM4 reload data D0 (LSB)

1 R/W

High Low

00FFB2

D7

D6

D5

D4

D3

D2

D1

D0

RDR57

RDR56

RDR55

RDR54

RDR53

RDR52

RDR51

RDR50

PTM5 reload data D7 (MSB)

PTM5 reload data D6

PTM5 reload data D5

PTM5 reload data D4

PTM5 reload data D3

PTM5 reload data D2

PTM5 reload data D1

PTM5 reload data D0 (LSB)

1 R/W

High Low

00FFB3

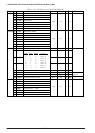

D7

D6

D5

D4

D3

D2

D1

D0

CDR57

CDR56

CDR55

CDR54

CDR53

CDR52

CDR51

CDR50

PTM5 compare data D7 (MSB)

PTM5 compare data D6

PTM5 compare data D5

PTM5 compare data D4

PTM5 compare data D3

PTM5 compare data D2

PTM5 compare data D1

PTM5 compare data D0 (LSB)

0 R/W

High Low

00FFB5

D7

D6

D5

D4

D3

D2

D1

D0

CDR47

CDR46

CDR45

CDR44

CDR43

CDR42

CDR41

CDR40

PTM4 compare data D7 (MSB)

PTM4 compare data D6

PTM4 compare data D5

PTM4 compare data D4

PTM4 compare data D3

PTM4 compare data D2

PTM4 compare data D1

PTM4 compare data D0 (LSB)

0 R/W

High Low

00FFB4