3-126 Vol. 2A CMPPD—Compare Packed Double-Precision Floating-Point Values

INSTRUCTION SET REFERENCE, A-M

CMPPD—Compare Packed Double-Precision Floating-Point Values

Description

Performs a SIMD compare of the two packed double-precision floating-point values in

the source operand (second operand) and the destination operand (first operand)

and returns the results of the comparison to the destination operand. The compar-

ison predicate operand (third operand) specifies the type of comparison performed

on each of the pairs of packed values. The result of each comparison is a quadword

mask of all 1s (comparison true) or all 0s (comparison false).

The source operand can be an XMM register or a 128-bit memory location. The desti-

nation operand is an XMM register. The comparison predicate operand is an 8-bit

immediate, the first 3 bits of which define the type of comparison to be made (see

Table 3-7). Bits 4 through 7 of the immediate are reserved.

Opcode Instruction 64-Bit

Mode

Compat/

Leg Mode

Description

66 0F C2 /r ib CMPPD xmm1,

xmm2/m128, imm8

Valid Valid Compare packed double-

precision floating-point

values in xmm2/m128 and

xmm1 using imm8 as

comparison predicate.

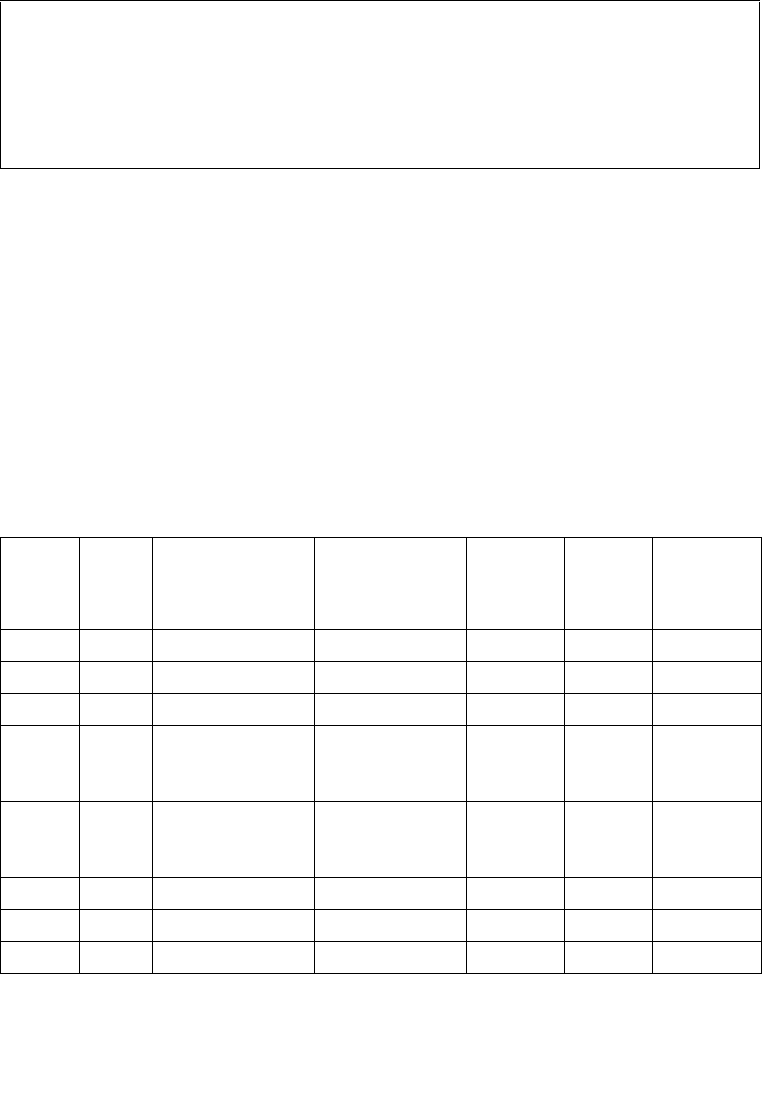

Table 3-7. Comparison Predicate for CMPPD and CMPPS Instructions

Predi-

cate

imm8

Encod-

ing

Description Relation where:

A Is 1st Operand

B Is 2nd

Operand

Emulation Result if

NaN

Operand

QNaN

Oper-and

Signals

Invalid

EQ 000B Equal A

= BFalseNo

LT 001B Less-than A < BFalseYes

LE 010B Less-than-or-equal A

≤ BFalseYes

Greater than A

> BSwap

Operands,

Use LT

False Yes

Greater-than-or-

equal

A

≥ BSwap

Operands,

Use LE

False Yes

UNORD 011B Unordered A, B = Unordered True No

NEQ 100B Not-equal A ≠ BTrueNo

NLT 101B Not-less-than NOT(A

< B) True Yes