3-2 Vol. 2A

INSTRUCTION SET REFERENCE, A-M

3.1.1.1 Opcode Column in the Instruction Summary Table

The “Opcode” column in the table above shows the object code produced for each

form of the instruction. When possible, codes are given as hexadecimal bytes in the

same order in which they appear in memory. Definitions of entries other than hexa-

decimal bytes are as follows:

• REX.W — Indicates the use of a REX prefix that affects operand size or

instruction semantics. The ordering of the REX prefix and other

optional/mandatory instruction prefixes are discussed Chapter 2. Note that REX

prefixes that promote legacy instructions to 64-bit behavior are not listed

explicitly in the opcode column.

• /digit — A digit between 0 and 7 indicates that the ModR/M byte of the

instruction uses only the r/m (register or memory) operand. The reg field

contains the digit that provides an extension to the instruction's opcode.

• /r — Indicates that the ModR/M byte of the instruction contains a register

operand and an r/m operand.

• cb, cw, cd, cp, co, ct — A 1-byte (cb), 2-byte (cw), 4-byte (cd), 6-byte (cp),

8-byte (co) or 10-byte (ct) value following the opcode. This value is used to

specify a code offset and possibly a new value for the code segment register.

• ib, iw, id, io — A 1-byte (ib), 2-byte (iw), 4-byte (id) or 8-byte (io) immediate

operand to the instruction that follows the opcode, ModR/M bytes or scale-

indexing bytes. The opcode determines if the operand is a signed value. All

words, doublewords and quadwords are given with the low-order byte first.

• +rb, +rw, +rd, +ro — A register code, from 0 through 7, added to the

hexadecimal byte given at the left of the plus sign to form a single opcode byte.

See Table 3-1 for the codes. The +ro columns in the table are applicable only in

64-bit mode.

• +i — A number used in floating-point instructions when one of the operands is

ST(i) from the FPU register stack. The number i (which can range from 0 to 7) is

added to the hexadecimal byte given at the left of the plus sign to form a single

opcode byte.

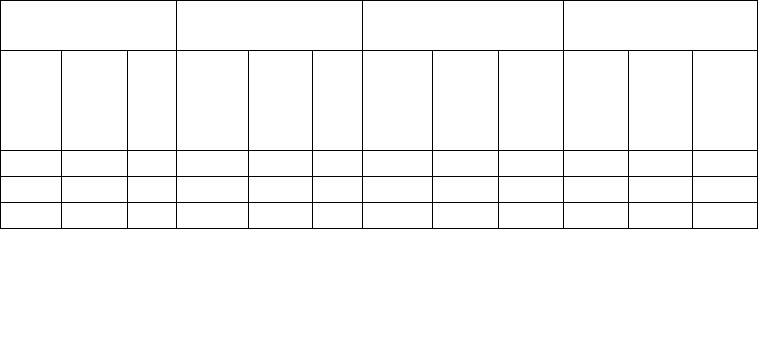

Table 3-1. Register Codes Associated With +rb, +rw, +rd, +ro

byte register word register dword register quadword register

(64-Bit Mode only)

Register

REX.B

Reg Field

Register

REX.B

Reg Field

Register

REX.B

Reg Field

Register

REX.B

Reg Field

AL None 0 AX None 0 EAX None 0 RAX None 0

CL None 1 CX None 1 ECX None 1 RCX None 1

DL None 2 DX None 2 EDX None 2 RDX None 2