Vol. 2A 3-381

INSTRUCTION SET REFERENCE, A-M

FSINCOS—Sine and Cosine

FSINCOS—Sine and Cosine

Description

Computes both the sine and the cosine of the source operand in register ST(0),

stores the sine in ST(0), and pushes the cosine onto the top of the FPU register stack.

(This instruction is faster than executing the FSIN and FCOS instructions in succes-

sion.)

The source operand must be given in radians and must be within the range −2

63

to

+2

63

. The following table shows the results obtained when taking the sine and cosine

of various classes of numbers, assuming that underflow does not occur.

If the source operand is outside the acceptable range, the C2 flag in the FPU status

word is set, and the value in register ST(0) remains unchanged. The instruction does

not raise an exception when the source operand is out of range. It is up to the

program to check the C2 flag for out-of-range conditions. Source values outside the

range −2

63

to +2

63

can be reduced to the range of the instruction by subtracting an

appropriate integer multiple of 2π or by using the FPREM instruction with a divisor of

2π. See the section titled “Pi” in Chapter 8 of the Intel® 64 and IA-32 Architectures

Software Developer’s Manual, Volume 1, for a discussion of the proper value to use

for π in performing such reductions.

This instruction’s operation is the same in non-64-bit modes and 64-bit mode.

Opcode Instruction 64-Bit

Mode

Compat/

Leg Mode

Description

D9 FB FSINCOS Valid Valid Compute the sine and cosine of ST(0);

replace ST(0) with the sine, and push the

cosine onto the register stack.

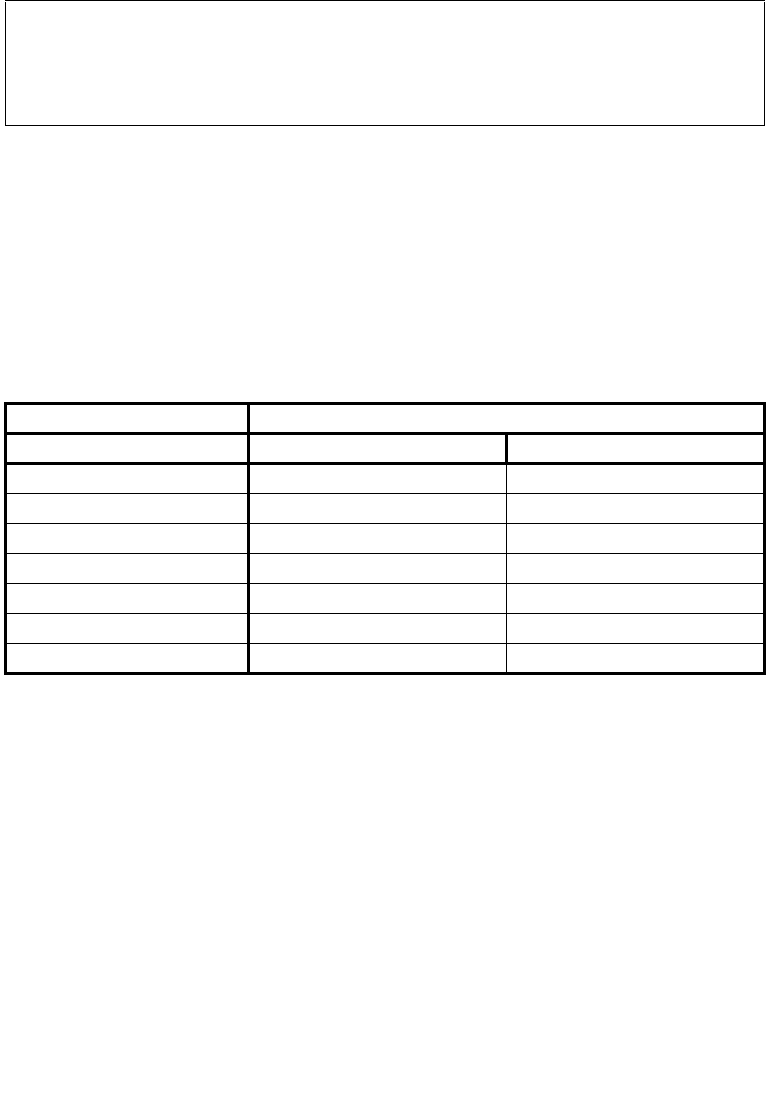

Table 3-41. FSINCOS Results

SRC DEST

ST(0) ST(1) Cosine ST(0) Sine

−∞ **

−

F −1 to +1 −1 to +1

−0 +1 −0

+0 +1 +0

+F −

1 to +1 −1 to +1

+∞ **

NaN

NaN

NaN

NOTES:

FMeans finite floating-point value.

* Indicates floating-point invalid-arithmetic-operand (#IA) exception.