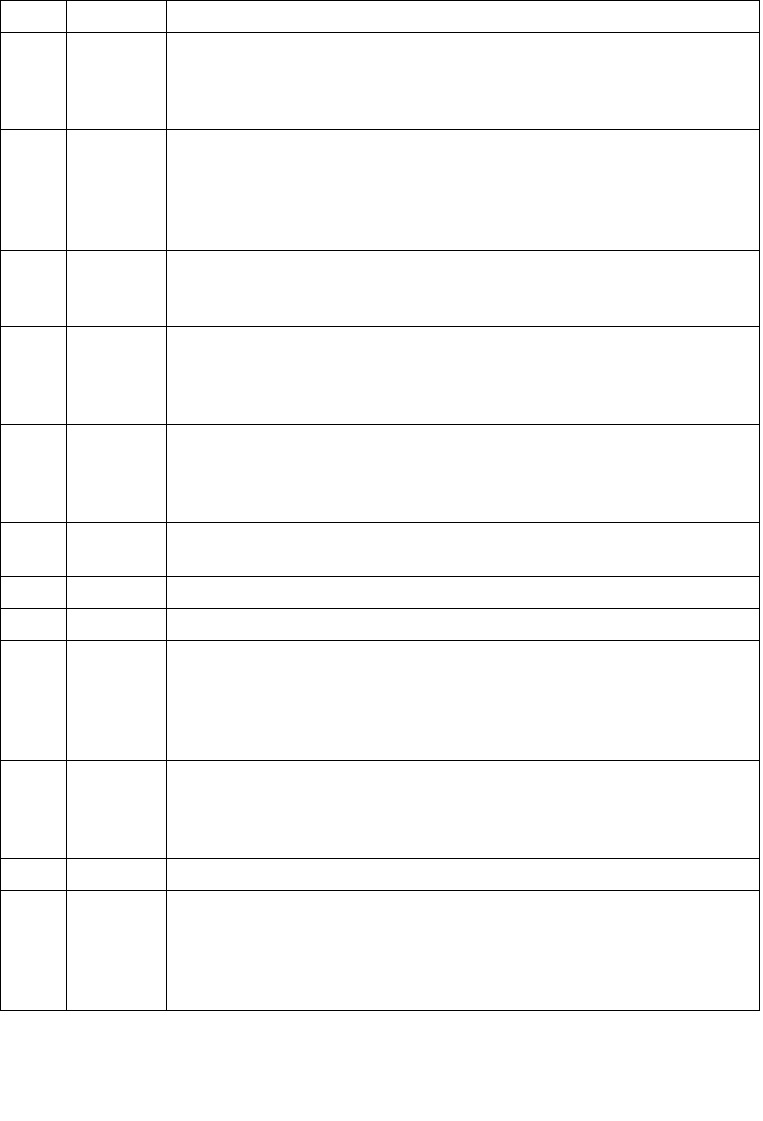

3-176 Vol. 2A CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-M

13 PGE PTE Global Bit. The global bit in page directory entries (PDEs) and page table

entries (PTEs) is supported, indicating TLB entries that are common to

different processes and need not be flushed. The CR4.PGE bit controls this

feature.

14 MCA Machine Check Architecture. The Machine Check Architecture, which

provides a compatible mechanism for error reporting in P6 family, Pentium 4,

Intel Xeon processors, and future processors, is supported. The MCG_CAP

MSR contains feature bits describing how many banks of error reporting

MSRs are supported.

15 CMOV Conditional Move Instructions. The conditional move instruction CMOV is

supported. In addition, if x87 FPU is present as indicated by the CPUID.FPU

feature bit, then the FCOMI and FCMOV instructions are supported

16 PAT Page Attribute Table. Page Attribute Table is supported. This feature

augments the Memory Type Range Registers (MTRRs), allowing an operating

system to specify attributes of memory on a 4K granularity through a linear

address.

17 PSE-36 36-Bit Page Size Extension. Extended 4-MByte pages that are capable of

addressing physical memory beyond 4 GBytes are supported. This feature

indicates that the upper four bits of the physical address of the 4-MByte

page is encoded by bits 13-16 of the page directory entry.

18 PSN Processor Serial Number. The processor supports the 96-bit processor

identification number feature and the feature is enabled.

19 CLFSH CLFLUSH Instruction. CLFLUSH Instruction is supported.

20 Reserved Reserved

21 DS Debug Store. The processor supports the ability to write debug information

into a memory resident buffer. This feature is used by the branch trace store

(BTS) and precise event-based sampling (PEBS) facilities (see Chapter 18,

“Debugging and Performance Monitoring,” in the Intel® 64 and IA-32

Architectures Software Developer’s Manual, Volume 3B).

22 ACPI Thermal Monitor and Software Controlled Clock Facilities. The processor

implements internal MSRs that allow processor temperature to be monitored

and processor performance to be modulated in predefined duty cycles under

software control.

23 MMX Intel MMX Technology. The processor supports the Intel MMX technology.

24 FXSR FXSAVE and FXRSTOR Instructions. The FXSAVE and FXRSTOR instructions

are supported for fast save and restore of the floating point context.

Presence of this bit also indicates that CR4.OSFXSR is available for an

operating system to indicate that it supports the FXSAVE and FXRSTOR

instructions.

Table 3-16. More on Feature Information Returned in the EDX Register (Contd.)

Bit # Mnemonic Description