3-418 Vol. 2A FXSAVE—Save x87 FPU, MMX Technology, SSE, and SSE2 State

INSTRUCTION SET REFERENCE, A-M

FXSAVE—Save x87 FPU, MMX Technology, SSE, and SSE2 State

Description

Saves the current state of the x87 FPU, MMX technology, XMM, and MXCSR registers

to a 512-byte memory location specified in the destination operand. The content

layout of the 512 byte region depends on whether the processor is operating in non-

64-bit operating modes or 64-bit sub-mode of IA-32e mode. The operation of

FXSAVE in non-64-bit modes are described first.

Non-64-Bit Mode Operation

Table 3-48 shows the layout of the state information in memory when the processor

is operating in legacy modes.

Opcode Instruction 64-Bit

Mode

Compat/

Leg Mode

Description

0F AE /0 FXSAVE m512byte Valid Valid Save the x87 FPU, MMX, XMM,

and MXCSR register state to

m512byte.

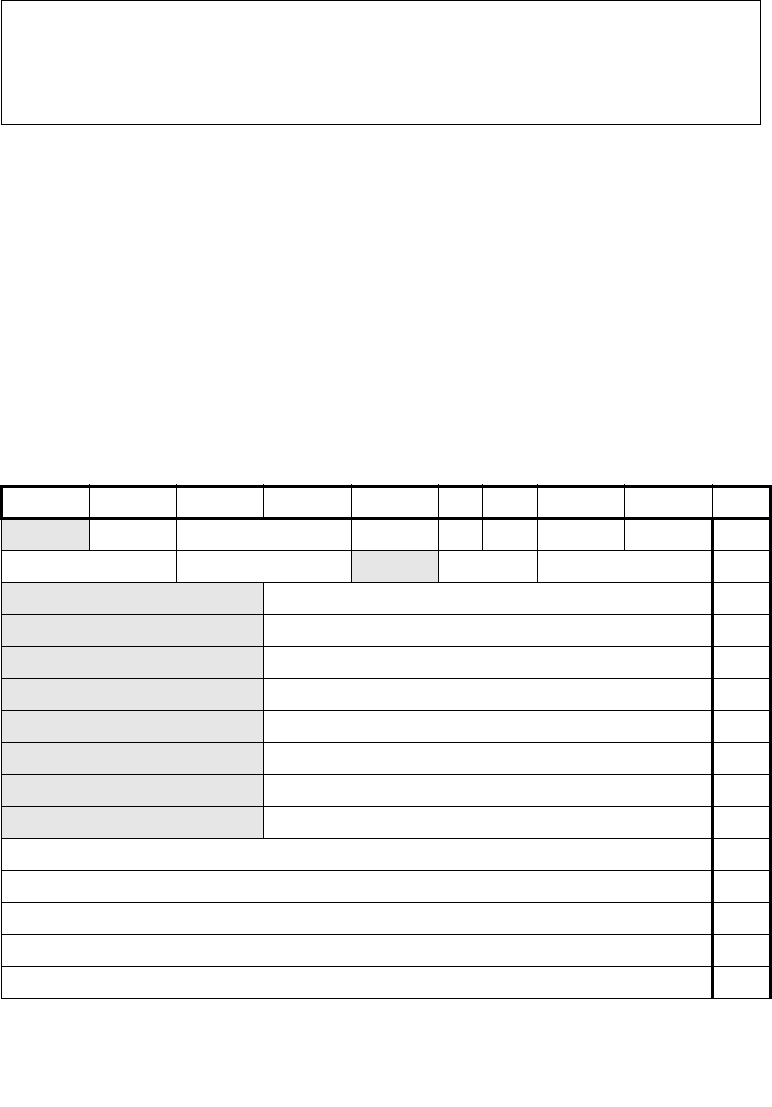

Table 3-48. Non-64-bit-Mode Layout of FXSAVE and FXRSTOR

Memory Region

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Rsrvd CS FPU IP FOP FTW FSW FCW 0

MXCSR_MASK MXCSR Rsrvd DS FPU DP 16

Reserved ST0/MM0 32

Reserved ST1/MM1 48

Reserved ST2/MM2 64

Reserved ST3/MM3 80

Reserved ST4/MM4 96

Reserved ST5/MM5 112

Reserved ST6/MM6 128

Reserved ST7/MM7 144

XMM0 160

XMM1 176

XMM2 192

XMM3 208

XMM4 224