Vol. 2A 3-177

INSTRUCTION SET REFERENCE, A-M

CPUID—CPU Identification

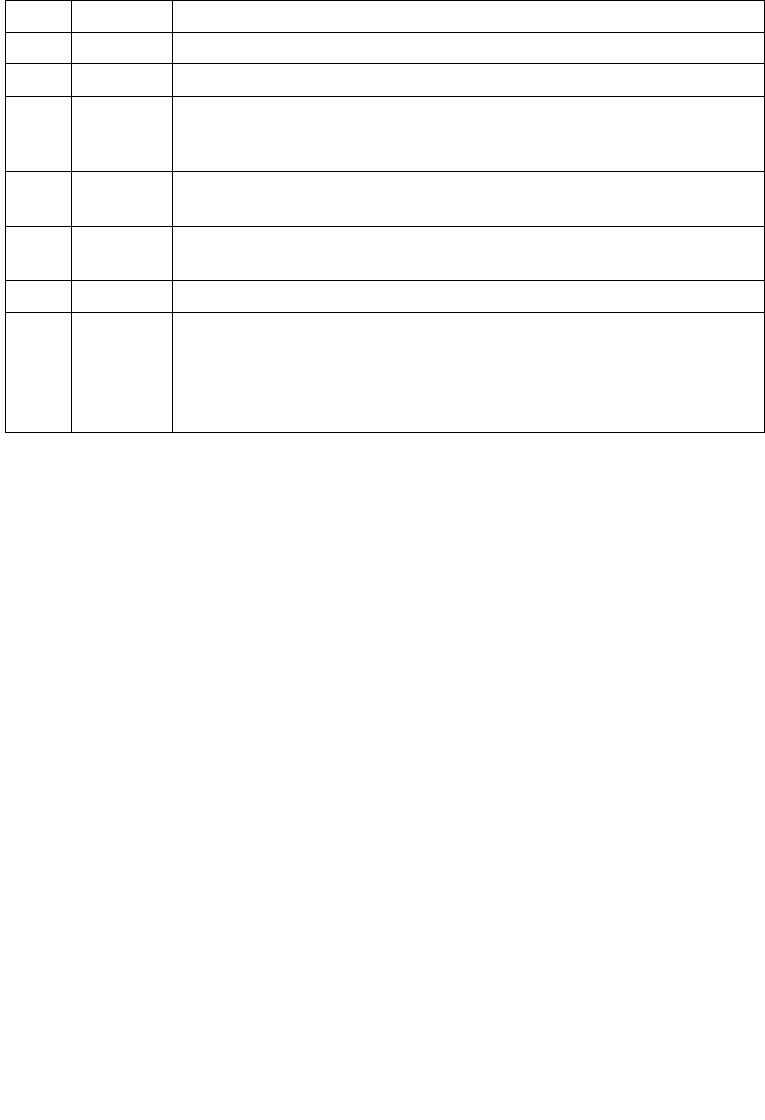

INPUT EAX = 2: Cache and TLB Information Returned in EAX, EBX, ECX, EDX

When CPUID executes with EAX set to 2, the processor returns information about the

processor’s internal caches and TLBs in the EAX, EBX, ECX, and EDX registers.

The encoding is as follows:

• The least-significant byte in register EAX (register AL) indicates the number of

times the CPUID instruction must be executed with an input value of 2 to get a

complete description of the processor’s caches and TLBs. The first member of the

family of Pentium 4 processors will return a 1.

• The most significant bit (bit 31) of each register indicates whether the register

contains valid information (set to 0) or is reserved (set to 1).

• If a register contains valid information, the information is contained in 1 byte

descriptors. Table 3-17 shows the encoding of these descriptors. Note that the

order of descriptors in the EAX, EBX, ECX, and EDX registers is not defined; that

is, specific bytes are not designated to contain descriptors for specific cache or

TLB types. The descriptors may appear in any order.

25 SSE SSE. The processor supports the SSE extensions.

26 SSE2 SSE2. The processor supports the SSE2 extensions.

27 SS Self Snoop. The processor supports the management of conflicting memory

types by performing a snoop of its own cache structure for transactions

issued to the bus.

28 HTT Multi-Threading. The physical processor package is capable of supporting

more than one logical processor.

29 TM Thermal Monitor. The processor implements the thermal monitor automatic

thermal control circuitry (TCC).

30 Reserved Reserved

31 PBE Pending Break Enable. The processor supports the use of the FERR#/PBE#

pin when the processor is in the stop-clock state (STPCLK# is asserted) to

signal the processor that an interrupt is pending and that the processor

should return to normal operation to handle the interrupt. Bit 10 (PBE

enable) in the IA32_MISC_ENABLE MSR enables this capability.

Table 3-16. More on Feature Information Returned in the EDX Register (Contd.)

Bit # Mnemonic Description