2-14 Vol. 2A

INSTRUCTION FORMAT

size of the memory offset follows the address-size default (64 bits in 64-bit mode).

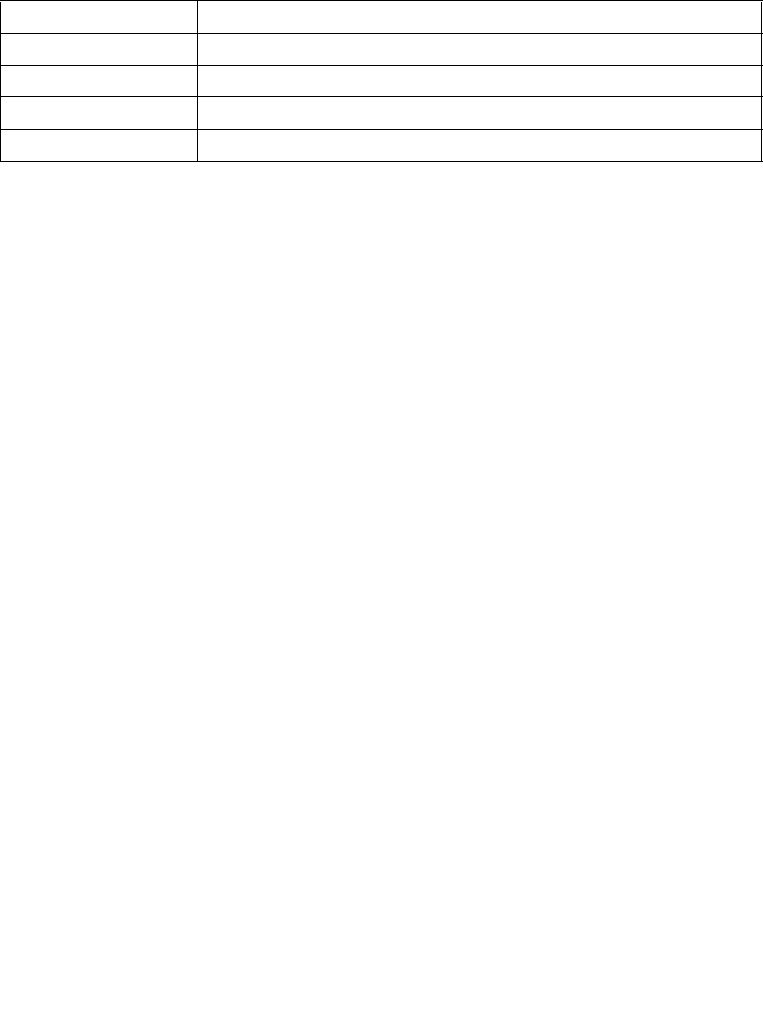

See Table 2-6.

2.2.1.5 Immediates

In 64-bit mode, the typical size of immediate operands remains 32 bits. When the

operand size is 64 bits, the processor sign-extends all immediates to 64 bits prior to

their use.

Support for 64-bit immediate operands is accomplished by expanding the semantics

of the existing move (MOV reg, imm16/32) instructions. These instructions (opcodes

B8H – BFH) move 16-bits or 32-bits of immediate data (depending on the effective

operand size) into a GPR. When the effective operand size is 64 bits, these instruc-

tions can be used to load an immediate into a GPR. A REX prefix is needed to override

the 32-bit default operand size to a 64-bit operand size.

For example:

48 B8 8877665544332211 MOV RAX,1122334455667788H

2.2.1.6 RIP-Relative Addressing

A new addressing form, RIP-relative (relative instruction-pointer) addressing, is

implemented in 64-bit mode. An effective address is formed by adding displacement

to the 64-bit RIP of the next instruction.

In IA-32 architecture and compatibility mode, addressing relative to the instruction

pointer is available only with control-transfer instructions. In 64-bit mode, instruc-

tions that use ModR/M addressing can use RIP-relative addressing. Without RIP-rela-

tive addressing, all ModR/M instruction modes address memory relative to zero.

RIP-relative addressing allows specific ModR/M modes to address memory relative to

the 64-bit RIP using a signed 32-bit displacement. This provides an offset range of

±2GB from the RIP. Table 2-7 shows the ModR/M and SIB encodings for RIP-relative

addressing. Redundant forms of 32-bit displacement-addressing exist in the current

ModR/M and SIB encodings. There is one ModR/M encoding and there are several SIB

encodings. RIP-relative addressing is encoded using a redundant form.

In 64-bit mode, the ModR/M Disp32 (32-bit displacement) encoding is re-defined to

be RIP+Disp32 rather than displacement-only. See Table 2-7.

Table 2-6. Direct Memory Offset Form of MOV

Opcode Instruction

A0 MOV AL, moffset

A1 MOV EAX, moffset

A2 MOV moffset, AL

A3 MOV moffset, EAX