Vol. 2A 3-15

INSTRUCTION SET REFERENCE, A-M

letter mnemonic with the corresponding interrupt vector number and exception

name. See Chapter 5, “Interrupt and Exception Handling,” in the Intel® 64 and IA-32

Architectures Software Developer’s Manual, Volume 3A, for a detailed description of

the exceptions.

Application programmers should consult the documentation provided with their oper-

ating systems to determine the actions taken when exceptions occur.

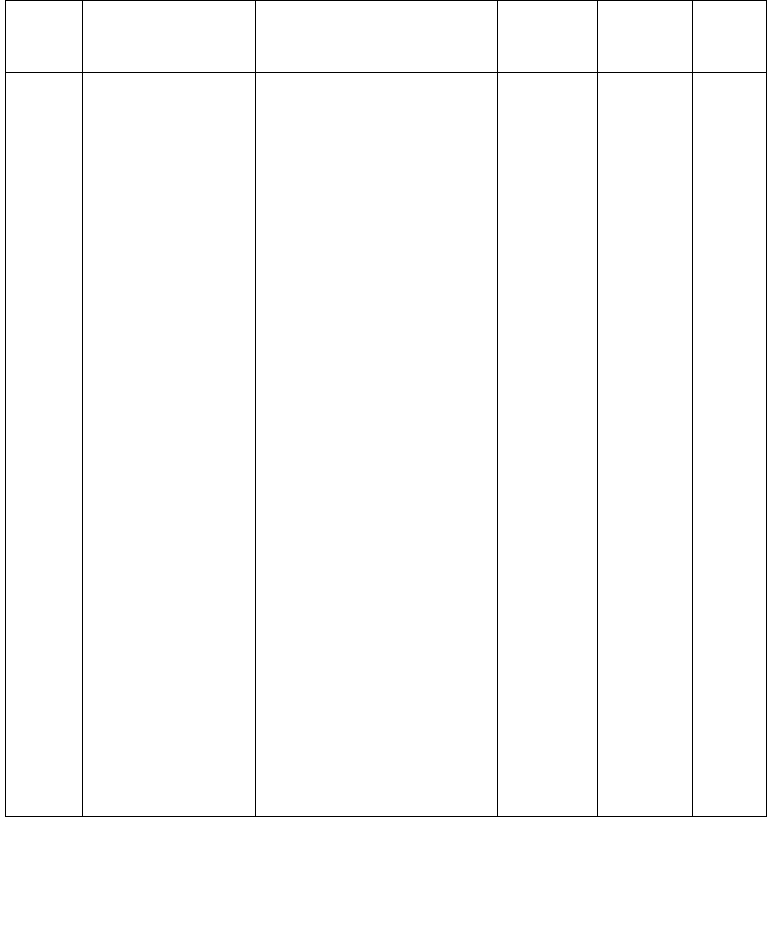

Table 3-3. Intel 64 and IA-32 General Exceptions

Vector

No.

Name Source Protected

Mode

1

Real

Address

Mode

Virtual

8086

Mode

0#DE—Divide ErrorDIV and IDIV instructions. Yes Yes Yes

1 #DB—Debug Any code or data reference. Yes Yes Yes

3 #BP—Breakpoint INT 3 instruction. Yes Yes Yes

4 #OF—Overflow INTO instruction. Yes Yes Yes

5 #BR—BOUND Range

Exceeded

BOUND instruction. Yes Yes Yes

6#UD—Invalid

Opcode (Undefined

Opcode)

UD2 instruction or reserved

opcode.

Yes Yes Yes

7 #NM—Device Not

Available (No Math

Coprocessor)

Floating-point or WAIT/FWAIT

instruction.

Yes Yes Yes

8 #DF—Double Fault Any instruction that can

generate an exception, an

NMI, or an INTR.

Yes Yes Yes

10 #TS—Invalid TSS Task switch or TSS access. Yes Reserved Yes

11 #NP—Segment Not

Present

Loading segment registers or

accessing system segments.

Yes Reserved Yes

12 #SS—Stack

Segment Fault

Stack operations and SS

register loads.

Yes Yes Yes

13 #GP—General

Protection

2

Any memory reference and

other protection checks.

Yes Yes Yes

14 #PF—Page Fault Any memory reference. Yes Reserved Yes

16 #MF—Floating-Point

Error (Math Fault)

Floating-point or WAIT/FWAIT

instruction.

Yes Yes Yes

17 #AC—Alignment

Check

Any data reference in

memory.

Yes Reserved Yes