Vol. 2A 3-423

INSTRUCTION SET REFERENCE, A-M

FXSAVE—Save x87 FPU, MMX Technology, SSE, and SSE2 State

The J-bit is defined to be the 1-bit binary integer to the left of the decimal place in the

significand. The M-bit is defined to be the most significant bit of the fractional portion

of the significand (i.e., the bit immediately to the right of the decimal place).

When the M-bit is the most significant bit of the fractional portion of the significand,

it must be 0 if the fraction is all 0’s.

IA-32e Mode Operation

In compatibility sub-mode of IA-32e mode, legacy SSE registers, XMM0 through

XMM7, are saved according to the legacy FXSAVE map. In 64-bit mode, all of the SSE

registers, XMM0 through XMM15, are saved. But the layout of the 64-bit FXSAVE map

has two flavors, depending on the value of the REX.W bit. The difference of these two

flavors is in the FPU IP and FPU DP pointers. When REX.W = 0, the FPU IP is saved as

CS with the 32 bit IP, and the FPU DP is saved as DS with the 32 bit DP. When REX.W

= 1, the FPU IP and FPU DP are both 64 bit values without and segment selectors.

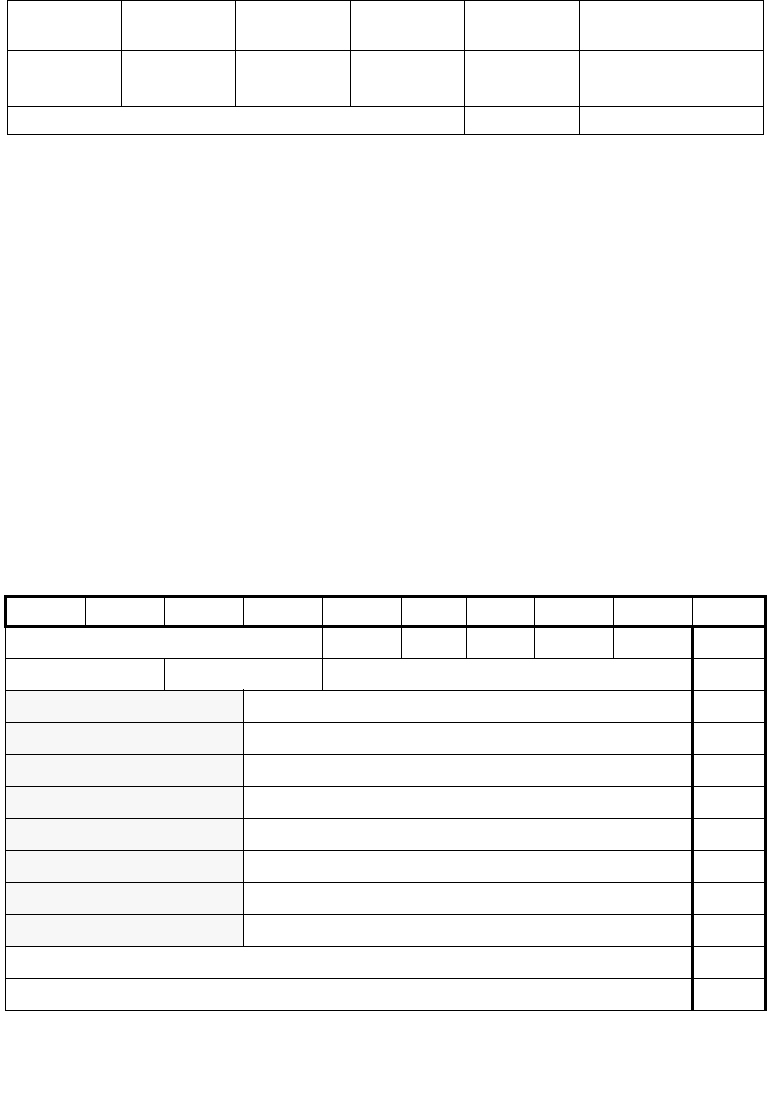

The IA-32e mode save formats are shown in Table 3-51 and Table 3-52 listed below.

101001Special10

101101Special10

For all legal combinations above. 0 Empty 11

Table 3-51. Layout of the 64-bit-mode FXSAVE Map

with Promoted OperandSize

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FPU IP FOP FTW FSW FCW 0

MXCSR_MASK MXCSR FPU DP 16

Reserved ST0/MM0 32

Reserved ST1/MM1 48

Reserved ST2/MM2 64

Reserved ST3/MM3 80

Reserved ST4/MM4 96

Reserved ST5/MM5 112

Reserved ST6/MM6 128

Reserved ST7/MM7 144

XMM0 160

XMM1 176

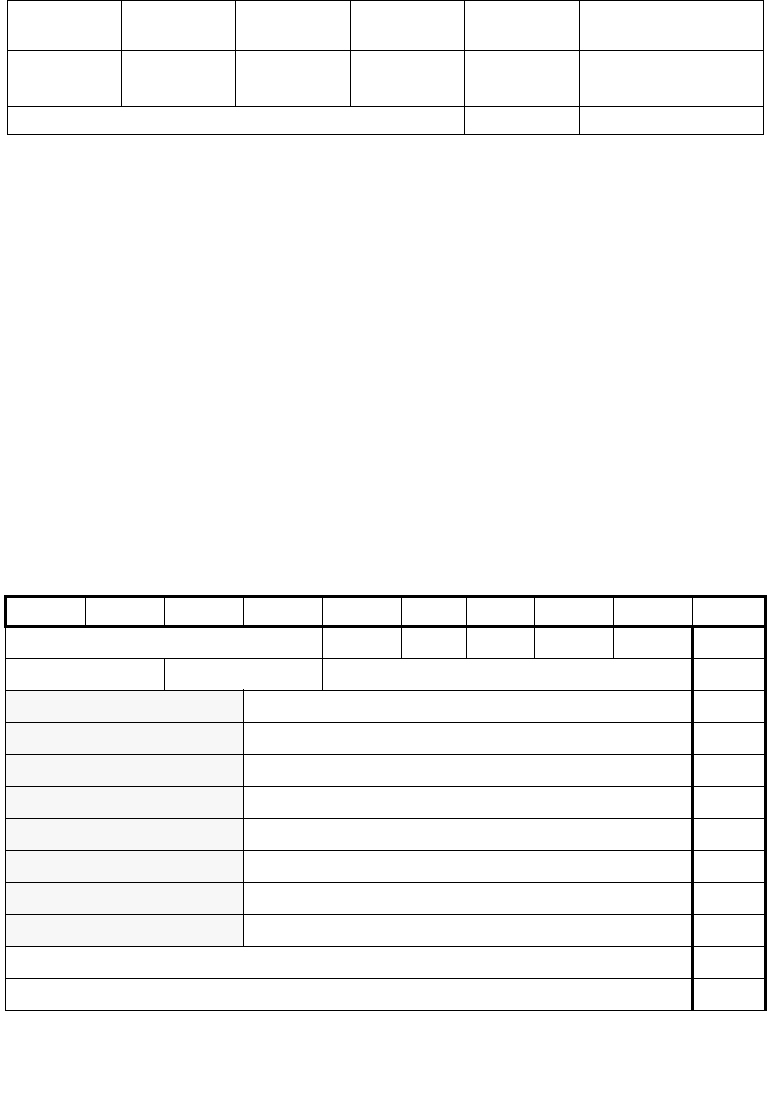

Table 3-50. Recreating FSAVE Format (Contd.)

Exponent

all 1’s

Exponent

all 0’s

Fraction

all 0’s

J and M

bits

FTW valid

bit x87 FTW