Vol. 2A 3-535

INSTRUCTION SET REFERENCE, A-M

LEA—Load Effective Address

LEA—Load Effective Address

Description

Computes the effective address of the second operand (the source operand) and

stores it in the first operand (destination operand). The source operand is a memory

address (offset part) specified with one of the processors addressing modes; the

destination operand is a general-purpose register. The address-size and operand-size

attributes affect the action performed by this instruction, as shown in the following

table. The operand-size attribute of the instruction is determined by the chosen

register; the address-size attribute is determined by the attribute of the code

segment.

Different assemblers may use different algorithms based on the size attribute and

symbolic reference of the source operand.

In 64-bit mode, the instruction’s destination operand is governed by operand size

attribute, the default operand size is 32 bits. Address calculation is governed by

address size attribute, the default address size is 64-bits. In 64-bit mode, address

size of 16 bits is not encodable. See Table 3-59.

Opcode Instruction 64-Bit

Mode

Compat/

Leg Mode

Description

8D /r LEA r16,m Valid Valid Store effective address for m in register

r16.

8D /r LEA r32,m Valid Valid Store effective address for m in register

r32.

REX.W + 8D /r LEA r64,m Valid N.E. Store effective address for m in register

r64.

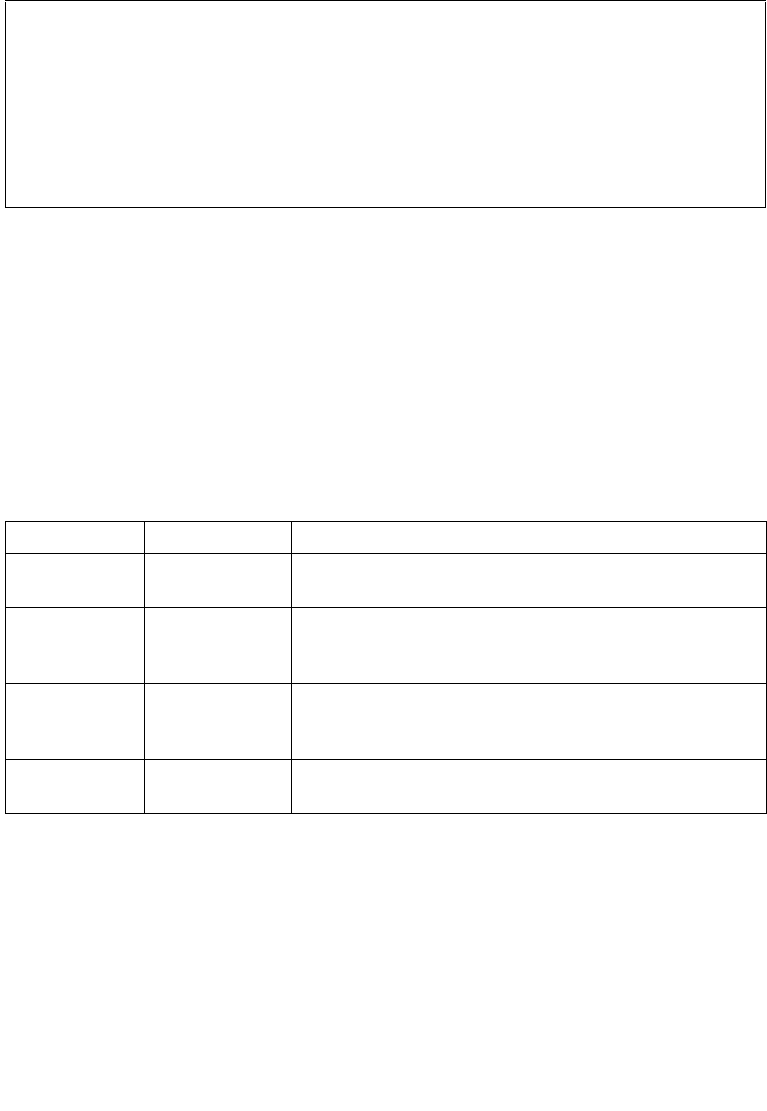

Table 3-58. Non-64-bit Mode LEA Operation with Address and Operand Size

Attributes

Operand Size Address Size Action Performed

16 16 16-bit effective address is calculated and stored in

requested 16-bit register destination.

16 32 32-bit effective address is calculated. The lower 16 bits of

the address are stored in the requested 16-bit register

destination.

32 16 16-bit effective address is calculated. The 16-bit address is

zero-extended and stored in the requested 32-bit register

destination.

32 32 32-bit effective address is calculated and stored in the

requested 32-bit register destination.