Vol. 2A 3-45

INSTRUCTION SET REFERENCE, A-M

ADDSUBPD—Packed Double-FP Add/Subtract

ADDSUBPD—Packed Double-FP Add/Subtract

Description

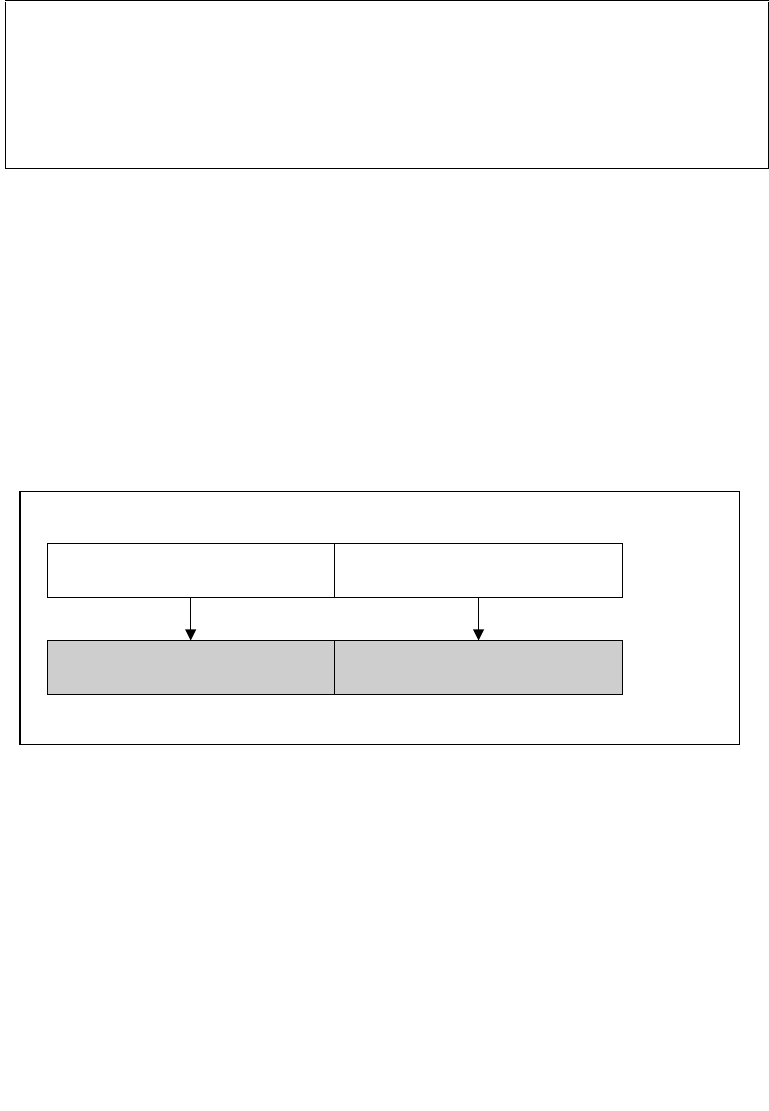

Adds the double-precision floating-point values in the high quadword of the source

and destination operands and stores the result in the high quadword of the destina-

tion operand.

Subtracts the double-precision floating-point value in the low quadword of the source

operand from the low quadword of the destination operand and stores the result in

the low quadword of the destination operand. See Figure 3-3.

The source operand can be a 128-bit memory location or an XMM register. The desti-

nation operand is an XMM register.

In 64-bit mode, using a REX prefix in the form of REX.R permits this instruction to

access additional registers (XMM8-XMM15).

Opcode Instruction 64-Bit

Mode

Compat/

Leg Mode

Description

66 0F D0 /r ADDSUBPD xmm1, xmm2/m128 Valid Valid Add/subtract

double-precision

floating-point values

from xmm2/m128

to xmm1.

Figure 3-3. ADDSUBPD—Packed Double-FP Add/Subtract

20

>@

[PP>@[PPP>@ [PP>@[PPP>@

>@

>@ >@

$''68%3'[PP[PPP

5(68/7

[PP

[PPP