Rev. 1.00, 05/04, page 89 of 544

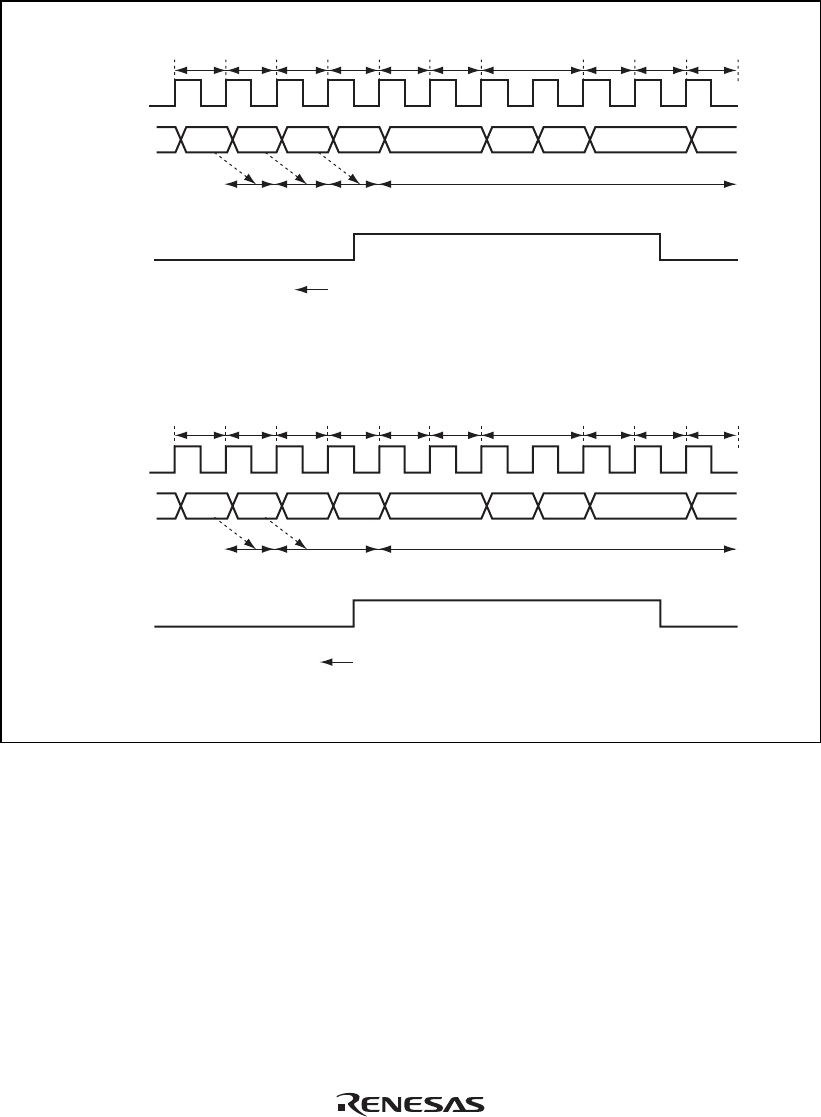

Figure 5.9 shows an example of address timing.

Instruction

fetch

Address bus

Break request

signal

Break point

NOP instruction is executed at break point address

H'0312 and following address H'0314.

Fetching is performed from address H'0316

after exception handling ends.

φ

Instruction

fetch

Instruction

fetch

Instruction

fetch

Instruction

fetch

Internal

operation

Internal

operation

Vector

fetch

Save

to stack

Instruction

fetch

H'0310

NOP

execution

H'0310 NOP

H'0312 NOP

H'0314 NOP

H'0316 NOP

NOP

execution

NOP

execution

Interrupt exception handling

H'0312 H'0314 H'0316 H'0318 H'0036SP-2 SP-4

(1) When a break address specified instruction is executed for one state in the program area and on-chip memory

Address bus

Break request

signal

Break point

MOV instruction is executed at break point address

H'0312, and NOP instruction is not executed

at the following address H'0314.

Fetching is performed from address H'0316

after exception handling ends.

φ

Instruction

fetch

Instruction

fetch

Instruction

fetch

Internal

operation

Internal

operation

Vector

fetch

Save

to stack

Instruction

fetch

H'0310

NOP

execution

H'0310 NOP

H'0312 MOV.W #xx:16,Rd

H'0316 NOP

H'0318 NOP

MOV.W

execution

Interrupt exception handling

H'0312 H'0314 H'0316 H'0318 H'0036SP-2 SP-4

(2) When a break address specified instruction is executed for two states in the program area and on-chip memory

Instruction

fetch

Instruction

fetch

Figure 5.9 Address Break Timing Example