Rev. 1.00, 05/04, page 345 of 544

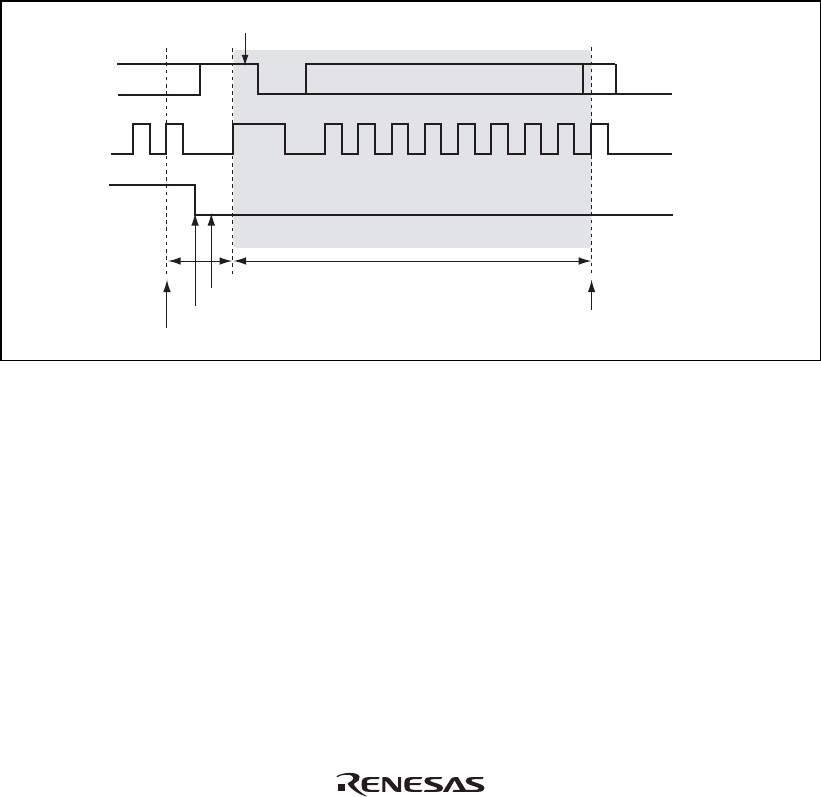

12. Note on TRS bit setting in slave mode

In I

2

C bus interface slave mode, if the TRS bit value in ICCR is set after detecting the rising

edge of the 9th clock pulse or the stop condition before detecting the next rising edge on the

SCL pin (the time indicated as (a) in figure 13.34), the bit value becomes valid immediately

when it is set. However, if the TRS bit is set during the other time (the time indicated as (b) in

figure 13.34), the bit value is suspended and remains invalid until the rising edge of the 9th

clock pulse or the stop condition is detected. Therefore, when the address is received after the

restart condition is input without the stop condition, the effective TRS bit value remains 1

(transmit mode) internally and thus the acknowledge bit is not transmitted after the address has

been received at the 9th clock pulse.

To receive the address in slave mode, clear the TRS bit to 0 during the time indicated as (a) in

figure 13.34. To release the SCL low level that is held by means of the wait function in slave

mode, clear the TRS bit to and then dummy-read ICDR.

Restart condition

Data

transmission

Address reception

SCL

TRS

TRS bit setting is suspended in this period

ICDR dummy read

TRS bit setting

(a) (b)

8

A

9 123456789

The rise of the 9th clock is detected

SDA

The rise of the 9th clock is detected

Figure 13.34 TRS Bit Set Timing in Slave Mode

Note: This restriction on usage can be canceled by setting the FNC1 and FNC0 bits to 1 in

ICXR.