Rev. 1.00, 05/04, page 19 of 544

The memory indirect addressing mode (@@aa:8) employed in the JMP and JSR instructions

uses an 8-bit absolute address included in the instruction code to specify a memory operand

that contains a branch address. In advanced mode, the operand is a 32-bit longword operand,

providing a 32-bit branch address. The upper 8 bits of these 32 bits are a reserved area that is

regarded as H'00. Branch addresses can be stored in the area from H'00000000 to H'000000FF.

Note that the top area of this range is also used for the exception vector table.

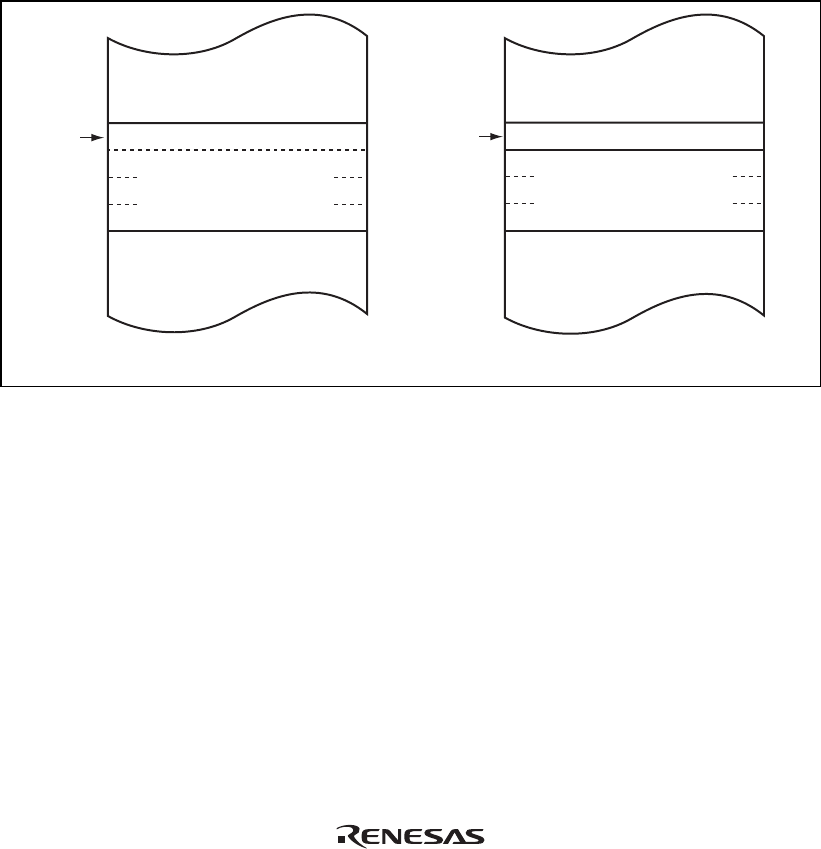

• Stack structure

In advanced mode, when the program counter (PC) is pushed onto the stack in a subroutine

call, and the PC and condition-code register (CCR) are pushed onto the stack in exception

handling, they are stored as shown in figure 2.4. The extended control register (EXR) is not

pushed onto the stack. For details, see section 4, Exception Handling.

(a) Subroutine Branch (b) Exception Handling

PC

(24 bits)

CCR

PC

(24 bits)

SP

SP

Reserved

Figure 2.4 Stack Structure in Advanced Mode