Rev. 1.00, 05/04, page 535 of 544

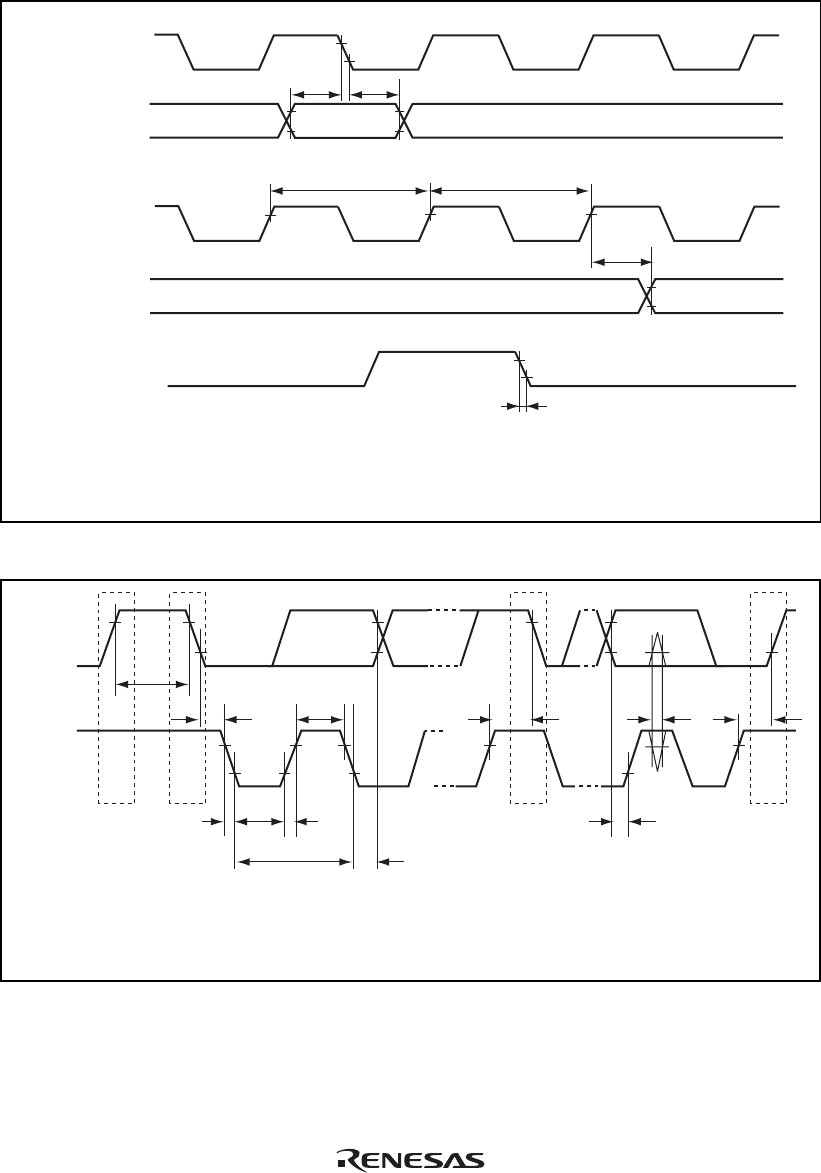

1. Reception

φ

KCLK/KD

*

KCLK/KD

*

t

KBIS

t

KBIH

Transmission (b)

t

KBF

2. Transmission (a)

φ

KCLK/KD

*

T

1

T

2

t

KBOD

Note: φ shown here is the clock scaled by 1/N when the operating mode is active

medium-speed mode.

* KCLK: PS2AC to PS2CC

KD: PS2AD to PS2CD

Figure 22.21 Keyboard Buffer Controller Timing

SDA0,

SDA1,

ExSDAA,

ExSDAB

V

IL

V

IH

t

BUF

P* P*S*

t

STAH

t

SCLH

t

Sr

t

SCLL

t

SCL

t

Sf

t

SDAH

Sr*

t

SDAS

t

STAS

t

SP

t

STOS

Note:* S, P, and Sr indicate the following conditions.

S:

P:

Sr:

Start condition

Stop condition

Retransmission start condition

SCL0,

SCL1,

ExSCLA,

ExSCLB

Figure 22.22 I

2

C Bus Interface Input/Output Timing