Rev. 1.00, 05/04, page 465 of 544

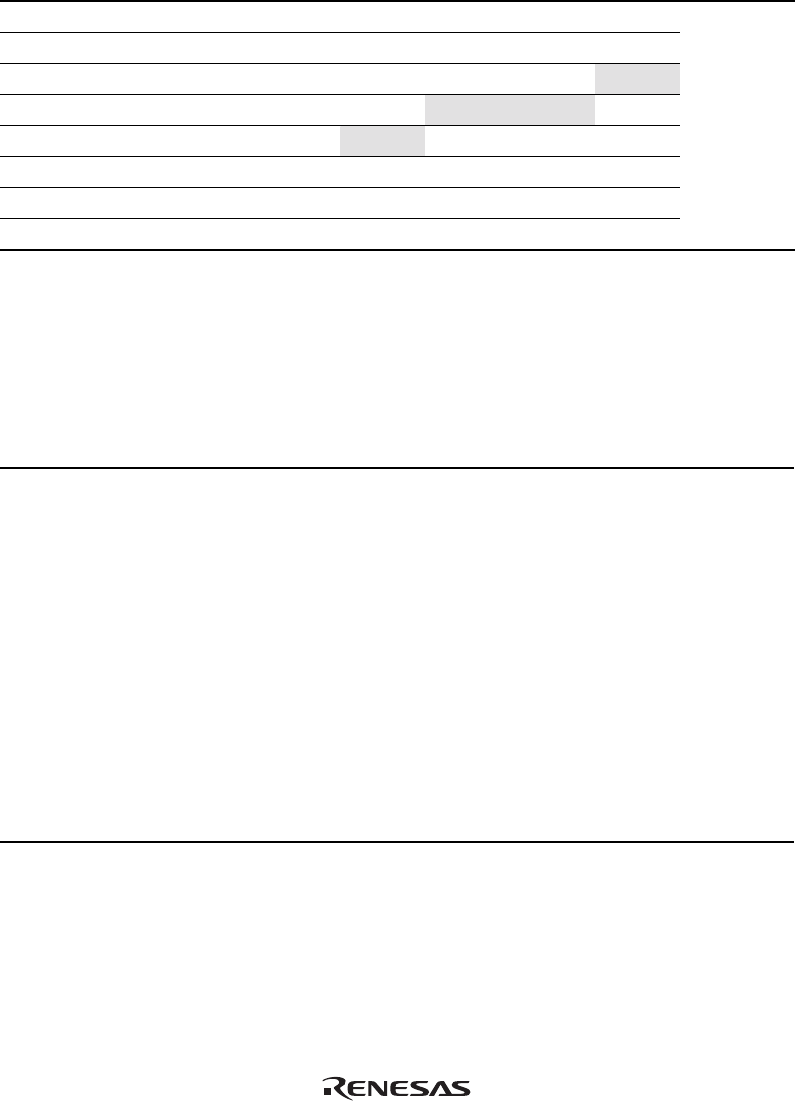

Table 20.1 Operating Frequency and Wait Time

STS2 STS1 STS0 Wait Time 10 MHz 8 MHz 6 MHz 4 MHz Unit

0 0 0 8192 states 0.8 1.0 1.3 20.

0 0 1 16384 states 1.6 2.0 2.7 4.1

0 1 0 32768 states 3.3 4.1 5.5 8.2

0 1 1 65536 states 6.6 8.2 10.9 16.4

1 0 0 131072 states 13.1 16.4 21.8 32.8

1 0 1 262144 states 26.2 32.8 43.6 65.6

1 1 0 Reserved

1 1 1 Reserved

ms

Shaded cells indicate the recommended specification.

20.1.2 Low-Power Control Register (LPWRCR)

LPWRCR controls power-down modes.

Bit Bit Name

Initial

Value R/W Description

7 DTON 0 R/W Direct Transfer On Flag

Specifies the operating mode to be entered after

executing the SLEEP instruction.

When the SLEEP instruction is executed in high-speed

mode or medium-speed mode:

0: Shifts to sleep mode, software standby mode, or

watch mode

1: Shifts directly to subactive mode, or shifts to sleep

mode or software standby mode

When the SLEEP instruction is executed in subactive

mode:

0: Shifts to subsleep mode or watch mode

1: Shifts directly to high-speed mode, or shifts to

subsleep mode