Rev. 1.00, 05/04, page 218 of 544

10.10.5 Switching of Internal Clocks and TCNT Operation

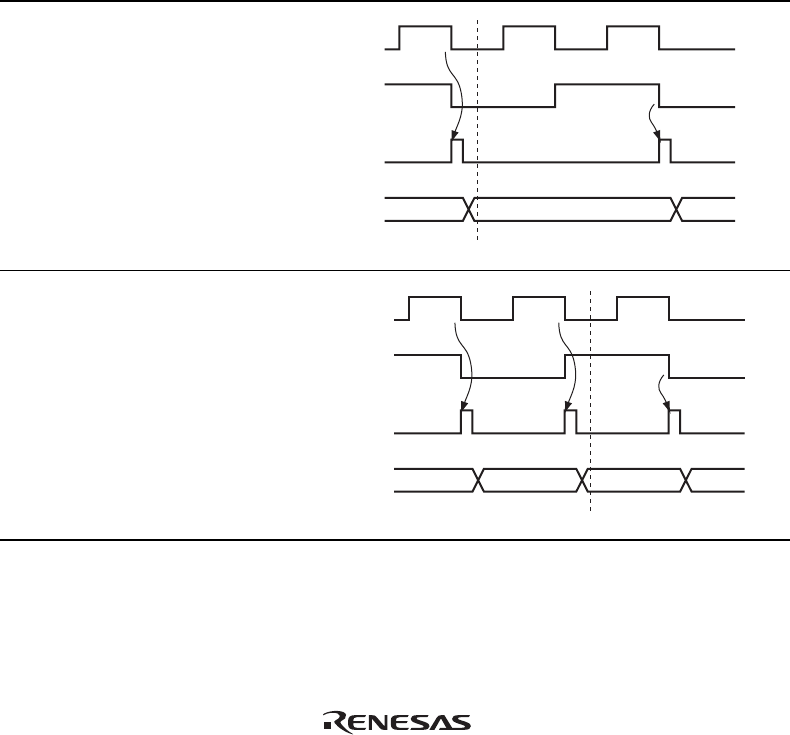

TCNT may increment erroneously when the internal clock is switched over. Table 10.9 shows the

relationship between the timing at which the internal clock is switched (by writing to the CKS1

and CKS0 bits) and the TCNT operation.

When the TCNT clock is generated from an internal clock, the falling edge of the internal clock

pulse is detected. If clock switching causes a change from high to low level, as shown in no. 3 in

table 10.9, a TCNT clock pulse is generated on the assumption that the switchover is a falling

edge, and TCNT is incremented.

Erroneous incrementation can also happen when switching between internal and external clocks.

Table 10.9 Switching of Internal Clocks and TCNT Operation

No.

Timing of Switchover

by Means of CKS1

and CKS0 Bits

TCNT Clock Operation

1 Clock switching from low to

low level*

1

Clock before

switchover

Clock after

switchover

TCNT

clock

TCNT

CKS bit rewrite

N N + 1

2 Clock switching from low to

high level∗

2

Clock before

switchover

Clock after

switchover

TCNT

clock

TCNT

CKS bit rewrite

N N + 1 N + 2