Rev. 1.00, 05/04, page 362 of 544

14.4.6 KBF Setting Timing and KCLK Control

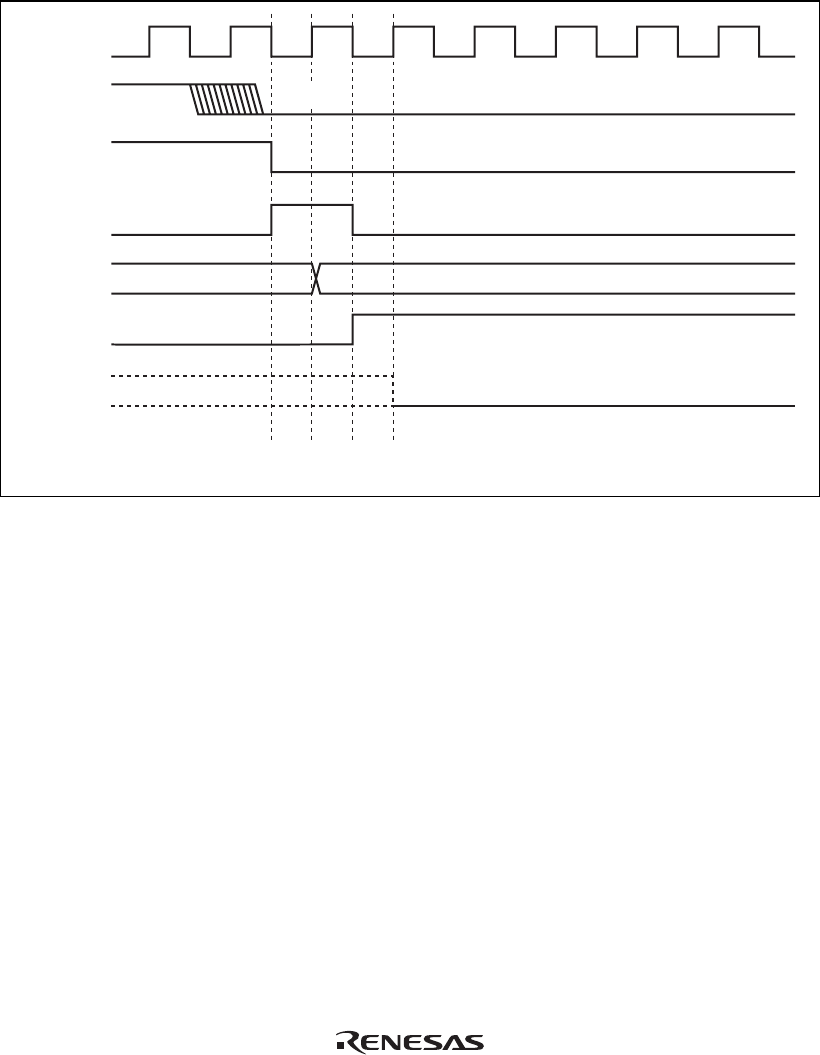

Figure 14.11 shows the KBF setting timing and the KCLK pin states.

KCLK

(pin)

φ

*

Internal

KCLK

Falling edge

signal

RXCR3 to

RXCR0

KCLK

(output)

KBF

11th fall

Automatic I/O inhibit

B'0000B'1010

Note: * The

φ

clock shown here is scaled by 1/N in medium-speed mode when the operating

mode is active mode.

Figure 14.11 KBF Setting and KCLK Automatic I/O Inhibit Generation Timing