Rev. 1.00, 05/04, page 261 of 544

12.5.2 Multiprocessor Serial Data Reception

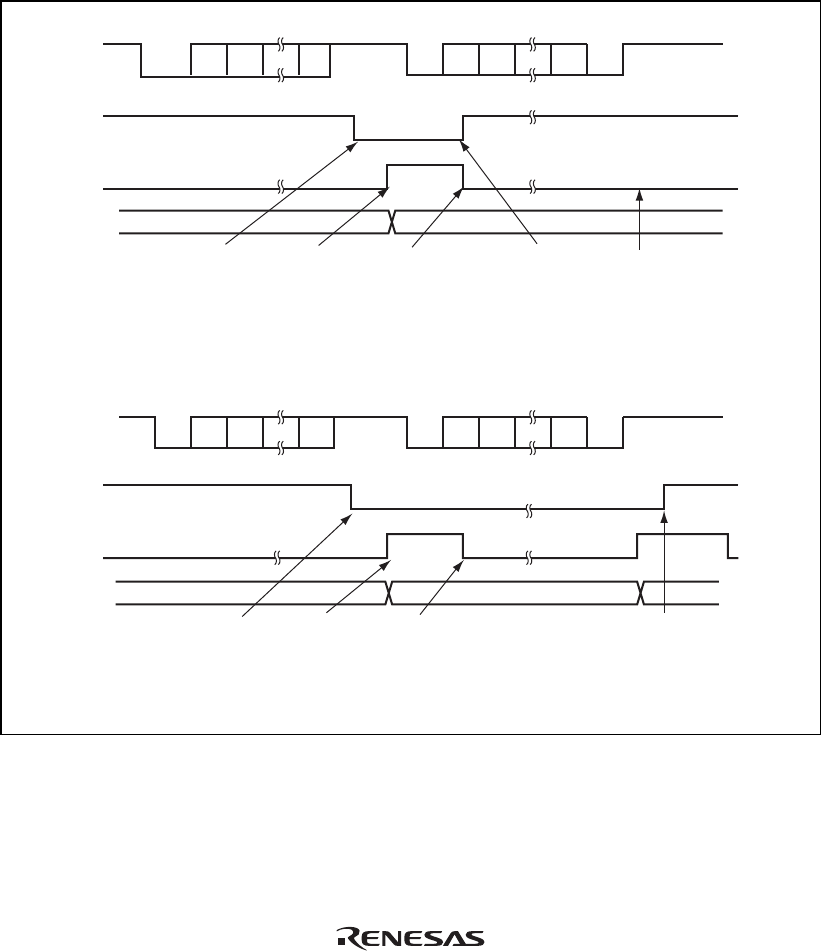

Figure 12.13 shows a sample flowchart for multiprocessor serial data reception. If the MPIE bit

in SCR is set to 1, data is skipped until data with a 1 multiprocessor bit is sent. On receiving data

with a 1 multiprocessor bit, the receive data is transferred to RDR. An RXI interrupt request is

generated at this time. All other SCI operations are the same as in asynchronous mode. Figure

12.12 shows an example of SCI operation for multiprocessor format reception.

MPIE

RDR

value

0 D0 D1 D7 1 1 0 D0 D1

D7

01

1

1

Data (ID1)Start

bit MPB

Stop

bit

Start

bit

Data (Data 1)

MPB

Stop

bit

Data (ID2)Start

bit

Stop

bit

Start

bit

Data (Data 2)

Stop

bit

RXI interrupt

request

(multiprocessor

interrupt)

generated

Idle state

(mark state)

RDRF

RDR data read

and RDRF flag

cleared to 0 in

RXI interrupt

handling routine

If not this station’s ID,

MPIE bit is set to 1

again

RXI interrupt request is

not generated, and RDR

retains its state

ID1

(a) Data does not match station’s ID

MPIE

RDR

value

0 D0 D1 D7 1 1 0 D0 D1

D7

01

1

1

MPB

MPB

RXI interrupt

request

(multiprocessor

interrupt)

generated

Idle state

(mark state)

RDRF

RDR data read and

RDRF flag cleared

to 0 in RXI interrupt

handling routine

Matches this station’s ID,

so reception continues, and

data is received in RXI

interrupt service routine

MPIE bit set to 1

again

ID2

(b) Data matches station’s ID

Data 2ID1

MPIE = 0

MPIE = 0

Figure 12.12 Example of SCI Receive Operation (Example with 8-Bit Data, Multiprocessor

Bit, One Stop Bit)