Rev. 1.00, 05/04, page 40 of 544

2.7 Addressing Modes and Effective Address Calculation

The H8S/2000 CPU supports the eight addressing modes listed in table 2.11. Each instruction uses

a subset of these addressing modes.

Arithmetic and logic operations instructions can use the register direct and immediate addressing

modes. Data transfer instructions can use all addressing modes except program-counter relative

and memory indirect. Bit manipulation instructions can use register direct, register indirect, or

absolute addressing mode to specify an operand, and register direct (BSET, BCLR, BNOT, and

BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

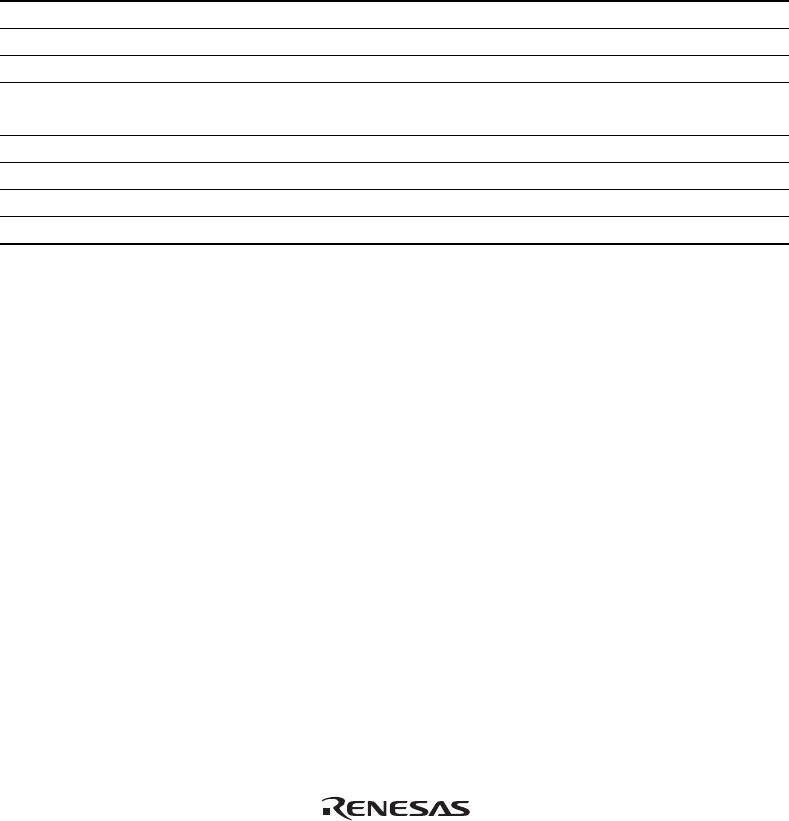

Table 2.11 Addressing Modes

No. Addressing Mode Symbol

1 Register direct Rn

2 Register indirect @ERn

3 Register indirect with displacement @(d:16,ERn)/@(d:32,ERn)

4 Register indirect with post-increment

Register indirect with pre-decrement

@ERn+

@–ERn

5 Absolute address @aa:8/@aa:16/@aa:24/@aa:32

6 Immediate #xx:8/#xx:16/#xx:32

7 Program-counter relative @(d:8,PC)/@(d:16,PC)

8 Memory indirect @@aa:8

2.7.1 Register Direct—Rn

The register field of the instruction code specifies an 8-, 16-, or 32-bit general register which

contains the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7

and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

2.7.2 Register Indirect—@ERn

The register field of the instruction code specifies an address register (ERn) which contains the

address of a memory operand. If the address is a program instruction address, the lower 24 bits are

valid and the upper 8 bits are all assumed to be 0 (H'00).