Rev. 1.00, 05/04, page 342 of 544

9. Note on when I

2

C bus interface stop condition instruction is issued

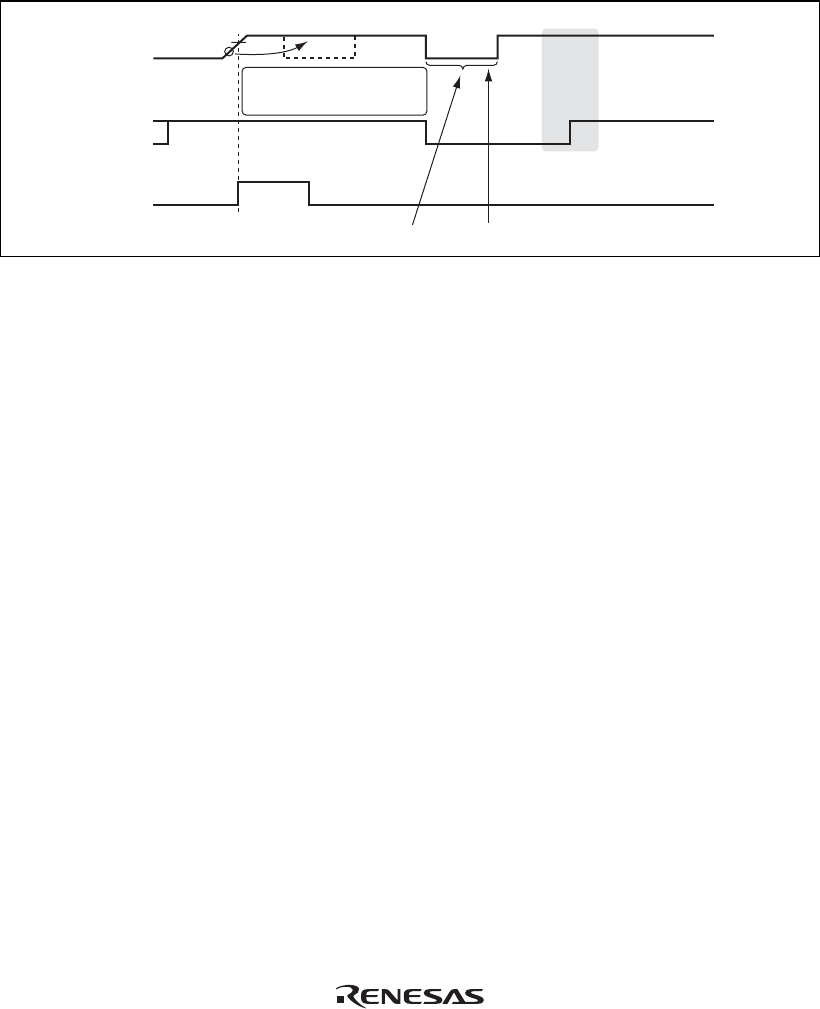

In cases where the rise time of the 9th clock of SCL exceeds the stipulated value because of a

large bus load capacity or where a slave device in which a wait can be inserted by driving the

SCL pin low is used, the stop condition instruction should be issued after reading SCL after the

rise of the 9th clock pulse and determining that it is low.

Stop condition generation

SCL

IRIC

[1] SCL = low determination

VIH

[2] Stop condition instruction issuance

SDA

9th clock

Secures a high period

SCL is detected as low

because the rise of the

waveform is delayed

Figure 13.31 Stop Condition Issuance Timing

Note: This restriction on usage can be canceled by setting the FNC1 and FNC0 bits to 1 in

ICXR.