Rev. 1.00, 05/04, page 173 of 544

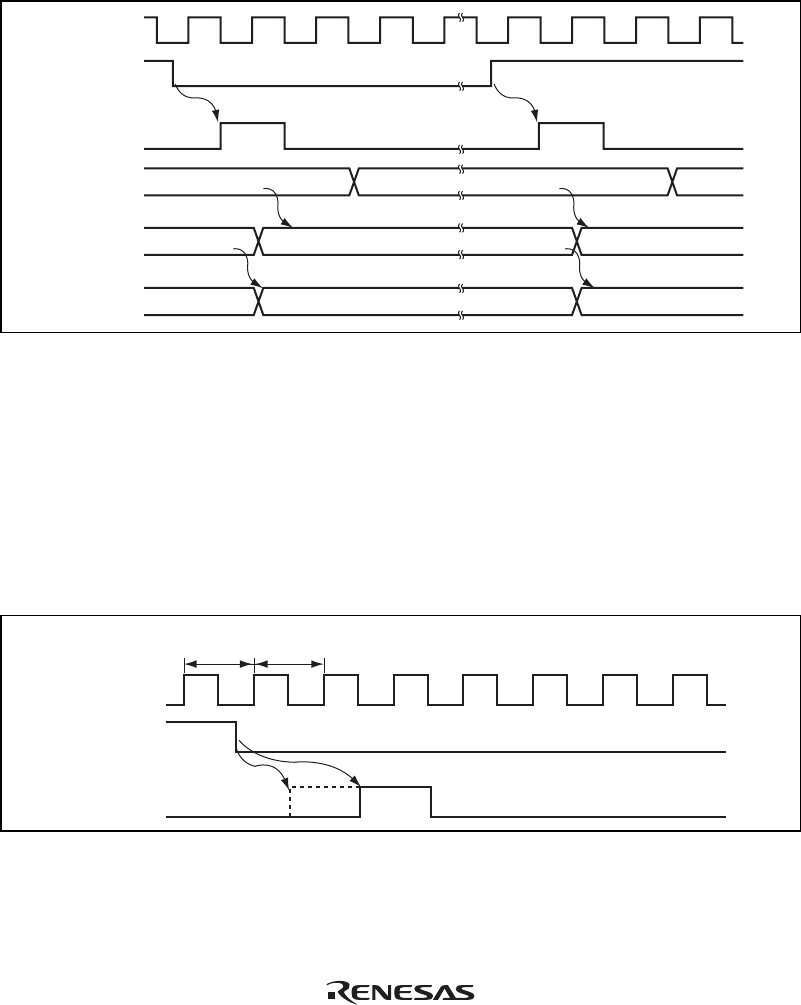

9.5.5 Buffered Input Capture Input Timing

ICRC and ICRD can operate as buffers for ICRA and ICRB, respectively. Figure 9.9 shows how

input capture operates when ICRC is used as ICRA's buffer register (BUFEA = 1) and IEDGA and

IEDGC are set to different values (IEDGA = 0 and IEDGC = 1, or IEDGA = 1 and IEDGC = 0),

so that input capture is performed on both the rising and falling edges of FTIA.

Input capture

signal

φ

FTIA

FRC

ICRA

ICRC

n n + 1 N + 1N

Mn

mM

n

M

N

n

Figure 9.9 Buffered Input Capture Timing

Even when ICRC or ICRD is used as a buffer register, its input capture flag is set by the selected

transition of its input capture signal. For example, if ICRC is used to buffer ICRA, when the edge

transition selected by the IEDGC bit occurs on the FTIC input capture line, ICFC will be set, and

if the ICICE bit is set at this time, an interrupt will be requested. The FRC value will not be

transferred to ICRC, however. In buffered input capture, if either set of two registers to which data

will be transferred (ICRA and ICRC, or ICRB and ICRD) is being read when the input capture

input signal arrives, input capture is delayed by one system clock (φ). Figure 9.10 shows the

timing when BUFEA = 1.

Input capture

signal

FTIA

φ

T

1

T

2

CPU read cycle of ICRA or ICRC

Figure 9.10 Buffered Input Capture Timing (BUFEA = 1)