Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 27

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

3.4 UART Interface

The UART interface are a 16550-compliant UART with the exception of transmit and

receive buffers. Transmit and receive buffers are 64 bytes-deep versus the 16 bytes

required by the 16550 UART specification.

The interface can be configured to support speeds from 1,200 Baud to 921 Kbaud. The

interface supports the following configurations:

• Five, six, seven, or eight data-bit transfers

• One or two stop bits

• Even, odd, or no parity

The request-to-send (RTS0_N) and clear-to-send (CTS0_N) modem control signals also

are available with the interface for hardware flow control. The hardware supports a

four-wire interface:

• Transmit Data

•Receive Data

•Request to Send

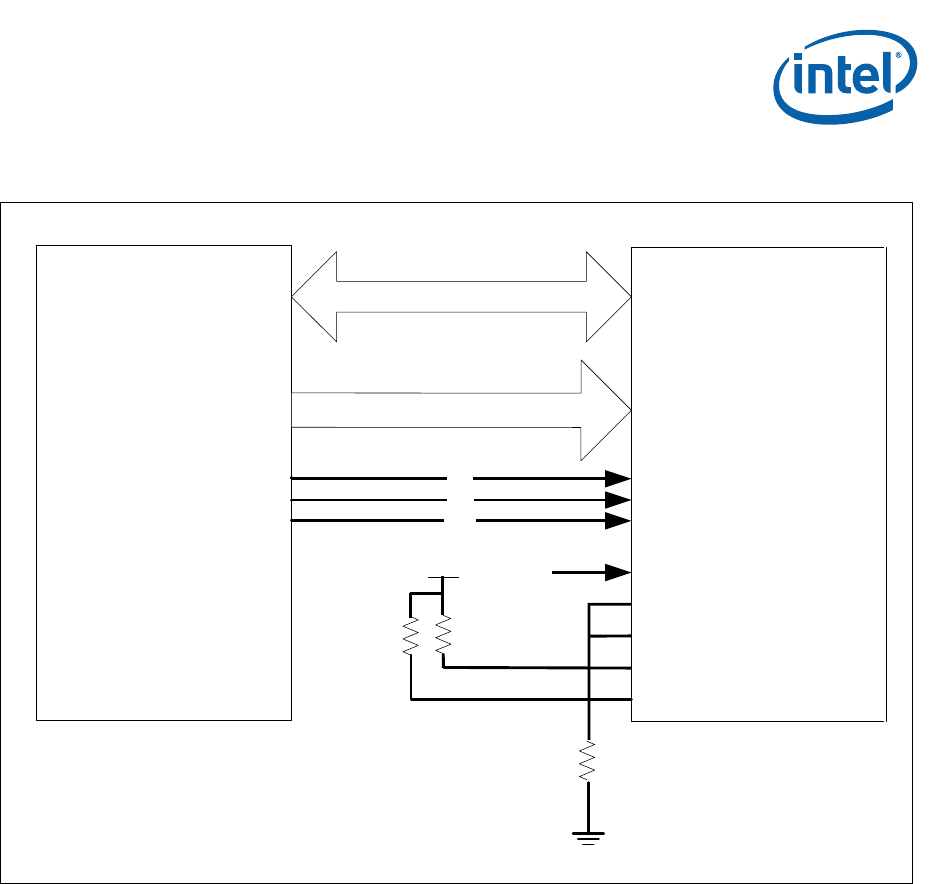

Figure 4. Flash Interface Example

E

X

_

A

D

D

R

[

2

3

:

0

]

EX_DATA[15:0]

16-Bit Device

16-Bit-Word Access

Intel

®

Flash

CS

OE

WR

EX_ADDR[23:0]

EX_DATA[15:0]

EX_CS_N

EX_RD_N

EX_WR_N

CE0

OE_N

WR_N

DATA[15:0]

ADDR[23:0]

CE1

CE2

RP_N

BYTE_N

VPEN_N

4.7 KΩ

RST#

3.3 V

4.7 KΩ

0 KΩ

Intel® IXP43X Product

Line of Network

Processors

B4097-005