Intel

®

IXP43X Product Line of Network Processors—Hardware Design Guidelines

Intel

®

IXP43X Product Line of Network Processors

HDG April 2007

68 Document Number: 316844; Revision: 001US

6.3 Clock Distribution

To meet timing and avoid clock overloading, it is recommended to use point-to-point

clock distribution as shown in Figure 24.

Clock skew between interfacing devices is very critical and must be met. The maximum

skew must be measured between any two components. If designing a motherboard,

the skew must be measured to the expansion card device and not to the PCI connector.

Ensure that clock skew between all devices does not exceed the values in Section 6.2.

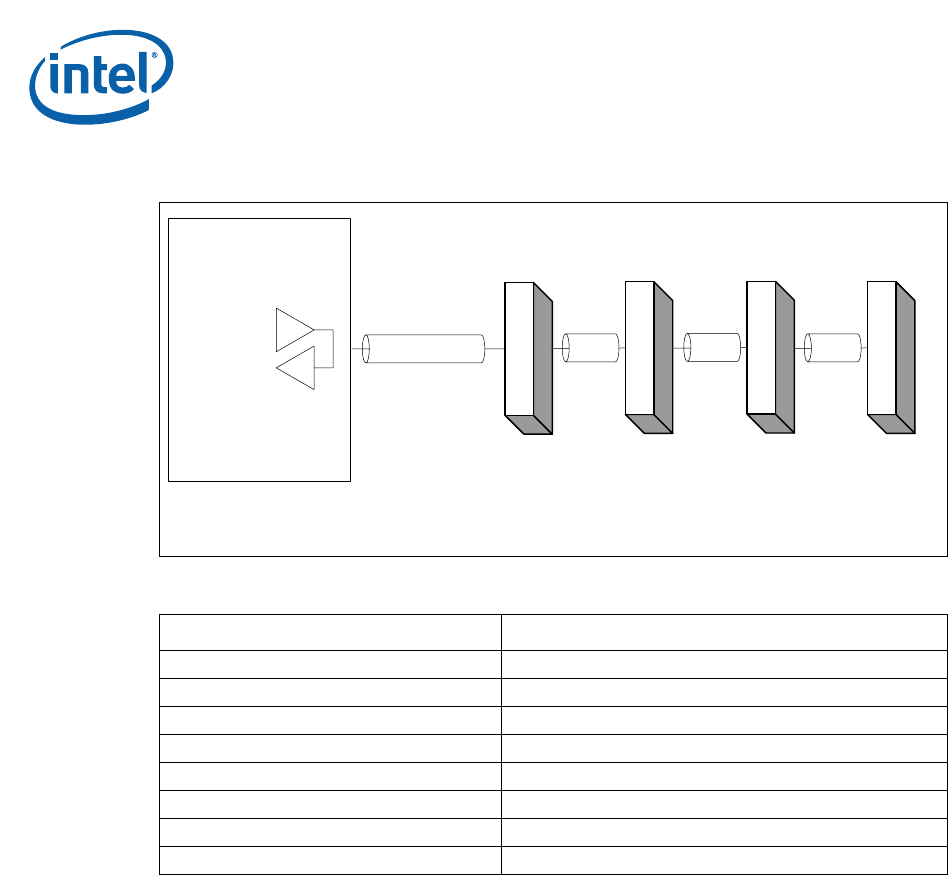

Figure 23. PCI Address/Data Topology

Table 22. PCI Address/Data Routing Guidelines

Parameter Routing Guidelines

Signal Group PCI Address/Data

Topology Daisy Chain

Reference Plane Ground

Characteristic Trace Impedance 55 Ω ±10%

Nominal Trace Width 5 mils

Nominal Trace Separation 10 mils

Spacing to Other Groups 20 mils

Limit the number of VIAS to 10 per Signal 10

Intel® IXP43X

Product Line of

Network

Processors

B5196-003

A

PCI Slot

BBB

PCI Slot PCI Slot PCI Slot