Intel

®

IXP43X Product Line of Network Processors—Hardware Design Guidelines

Intel

®

IXP43X Product Line of Network Processors

HDG April 2007

34 Document Number: 316844; Revision: 001US

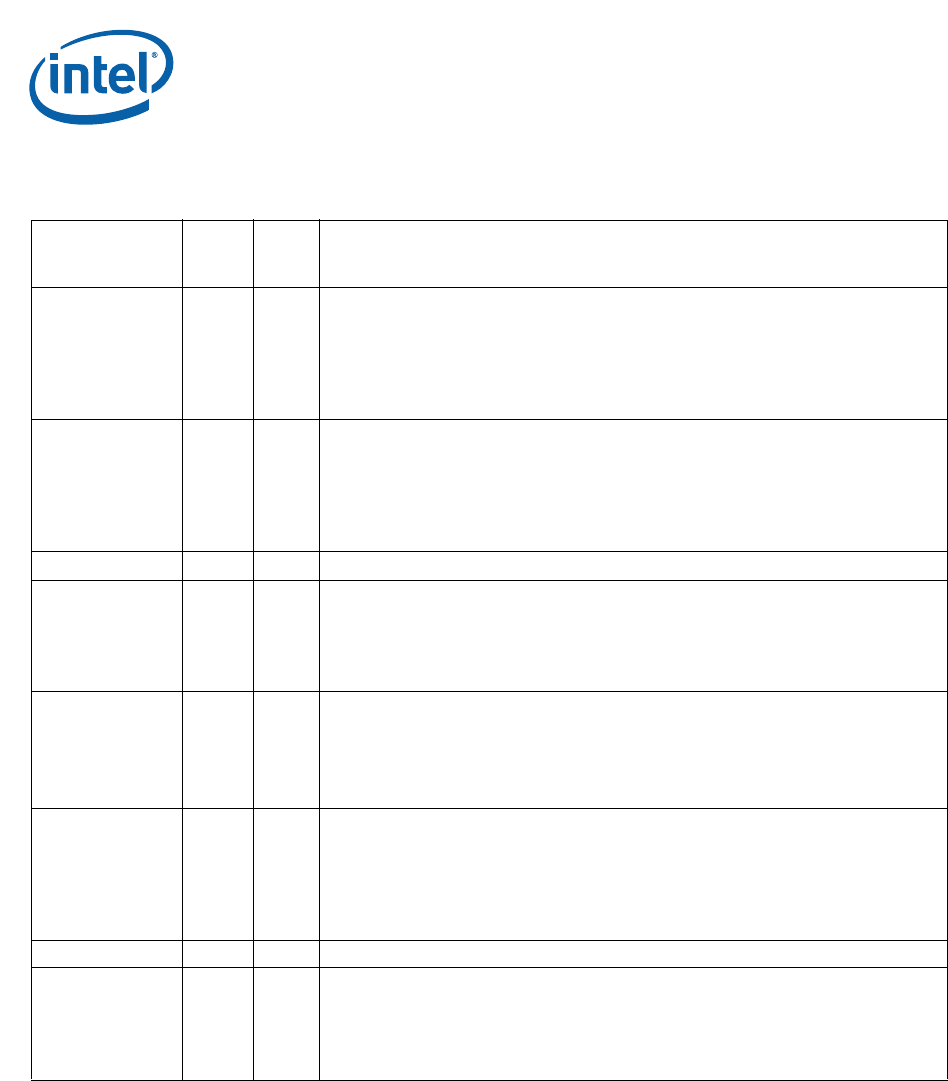

3.7.1 Signal Interface

Table 13. USB Host Signal Recommendations

A typical implementation of a USB interface Host down-stream is shown in Figure 9.

The Host controller cannot be used as a Device controller.

Note: Depending on the data rate required, Low-speed, Full-speed or High-speed, the 1.5K

resistor shown near the device interface must be connected on the D+ or D-.

Speed configuration at the Device can be set as stated in note 1 and 2 below. For more

details, refer to the Universal Serial Bus Specification, Revision 2.0.

Note:

1. If a 1.5-KΩ, pull-up resistor is connected to USB_P_POS line, the USB port is

identified as Full-speed and High-speed mode.

Name

Type

Field

Pull

Up/

Down

Description

USB_P0_POS I/O Yes

Positive signal of the differential USB receiver/driver for the USB host interface.

Use an 20Ω series termination resistor at the source.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse and is not being used in a system design, it

is not required for any connection. Refer to Expansion Bus Controller chapter of the

Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.

USB_P0_NEG I/O Yes

Negative signal of the differential USB receiver/driver for the USB host interface.

Use an 20Ω series termination resistor at the source.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse and is not being used in a system design, it

is not required for any connection. Refer to Expansion Bus Controller chapter of the

Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.

USB_P0_PWREN O No Enables the external VBUS power source.

USB_P0_OC I No

External VBUS power is in over current condition

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse and is not being used in a system design, it

is not required for any connection. Refer to Expansion Bus Controller chapter of the

Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.

USB_P1_POS I/O Yes

Positive signal of the differential USB receiver/driver for the USB host interface.

Use an 20Ω series termination resistor at the source.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse. Refer to Expansion Bus Controller chapter

of the Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.

USB_P1_NEG I/O Yes

Negative signal of the differential USB receiver/driver for the USB host interface.

Use an 20Ω series termination resistor at the source.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse and is not being used in a system design, it

is not required for any connection. Refer to Expansion Bus Controller chapter of the

Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.

USB_P1_PWREN O No Enable the external VBUS power source.

USB_P1_OC I No

External VBUS power is in over current condition

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled low with a 10-KΩ resistor. When this interface is

disabled through the USB Device soft fuse and is not being used in a system design, it

is not required for any connection. Refer to Expansion Bus Controller chapter of the

Intel

®

IXP43X Product Line of Network Processors Developer’s Manual.