Intel

®

IXP43X Product Line of Network Processors

April 2007 HDG

Document Number: 316844; Revision: 001US 39

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

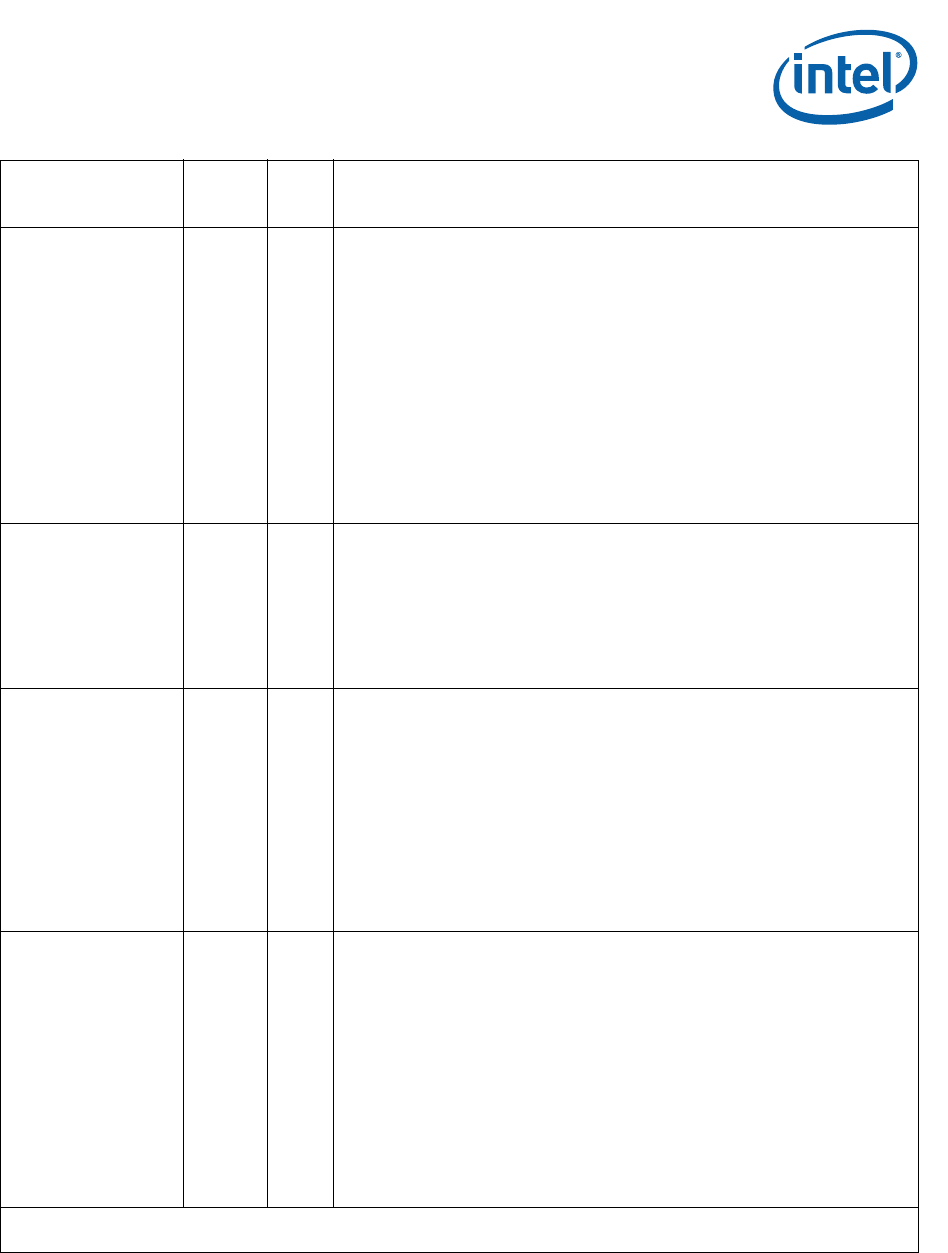

UTP_IP_FCI I Yes

UTOPIA Level 2 Input Data flow control input signal. Also known as RXEMPTY/

CLAV.

Used to inform the processor of the ability of each polled PHY to send a complete

cell. For cell-level flow control in an MPHY environment, RxClav is an active high

tri-stateable signal from the MPHY to ATM layer. The UTP_IP_FCI, which is

connected to multiple MPHY devices, sees logic high generated by the PHY, one

clock after the given PHY address is asserted, when a full cell can be received by

the PHY. The UTP_IP_FCI sees a logic low generated by the PHY, one clock cycle

after the PHY address is asserted if a full cell cannot be received by the PHY.

In a SPHY mode, this signal is used to indicate to the processor that the PHY has

an octet or cell available for transferring to the processor.

When this interface/signal is enabled and is not being used in a system design,

the interface/signal should be pulled high with a 10-KΩ resistor. When this

interface is disabled through the UTOPIA Level 2 and/or the NPE-A Ethernet soft

fuse (refer to Expansion Bus Controller chapter of the Intel

®

IXP43X Product Line

of Network Processors Developer’s Manual) and is not being used in a system

design, the interface/signal is not required for any connection.

UTP_IP_SOC I Yes

Start of Cell. RX_SOC

Active-high signal that is asserted when UTP_IP_DATA contains the first valid

byte of a transmitted cell.

When this interface/signal is enabled and is not being used in a system design,

the interface/signal should be pulled high with a 10KΩ resistor. When this

interface is disabled through the UTOPIA Level 2 and/or the NPE-A Ethernet soft

fuse and is not being used in a system design, it is not required for any

connection. Refer to Expansion Bus Controller chapter of the Intel

®

IXP43X

Product Line of Network Processors Developer’s Manual.

UTP_IP_DATA[3:0] /

ETHA_RXDATA[3:0]

IYes

UTOPIA Level 2 Mode of Operation:

UTOPIA Level 2 input data. Also known as RX_DATA.

Used by the processor to receive data from an ATM UTOPIA Level 2-compliant

PHY.

MII Mode of Operation:

Receives data bus from the PHY; asserted synchronously with respect to

ETHA_RXCLK.

When the interface/signal is enabled and is not being used in a system design, it

should be pulled high with a 10KΩ resistor.

When the interface is disabled through the UTOPIA Level 2 and/or the NPE-A

Ethernet soft fuse and is not being used in a system design, it is not required for

any connection. (Refer to Expansion Bus Controller chapter of the Intel

®

IXP43X

Product Line of Network Processors Developer’s Manual).

UTP_IP_DATA[4] /

ETHA_RXDV

IYes

UTOPIA Level 2 Mode of Operation:

UTOPIA Level 2 input data. Also known as RX_DATA.

Used by to the processor to receive data from an ATM UTOPIA Level 2-compliant

PHY.

MII Mode of Operation:

Receive data valid used to inform the MII interface about data that is being sent

by the Ethernet PHY.

This MAC does not contain hardware hashing capabilities that are local to the

interface.

When the interface/signal is enabled and is not being used in a system design,

the interface/signal should be pulled high with a 10-KΩ resistor. When this

interface is disabled through the UTOPIA Level 2 and/or the NPE-A Ethernet soft

fuse (and is not being used in a system design, it is not required for any

connection. Refer to Expansion Bus Controller chapter of the Intel

®

IXP43X

Product Line of Network Processors Developer’s Manual.

Name

Type

Field

Pull

Up/

Down

Description

†† Refer to the Intel

®

IXP43X Product Line of Network Processors Developer’s Manual for information on how to select an

interface.