Intel

®

IXP43X Product Line of Network Processors—Hardware Design Guidelines

Intel

®

IXP43X Product Line of Network Processors

HDG April 2007

30 Document Number: 316844; Revision: 001US

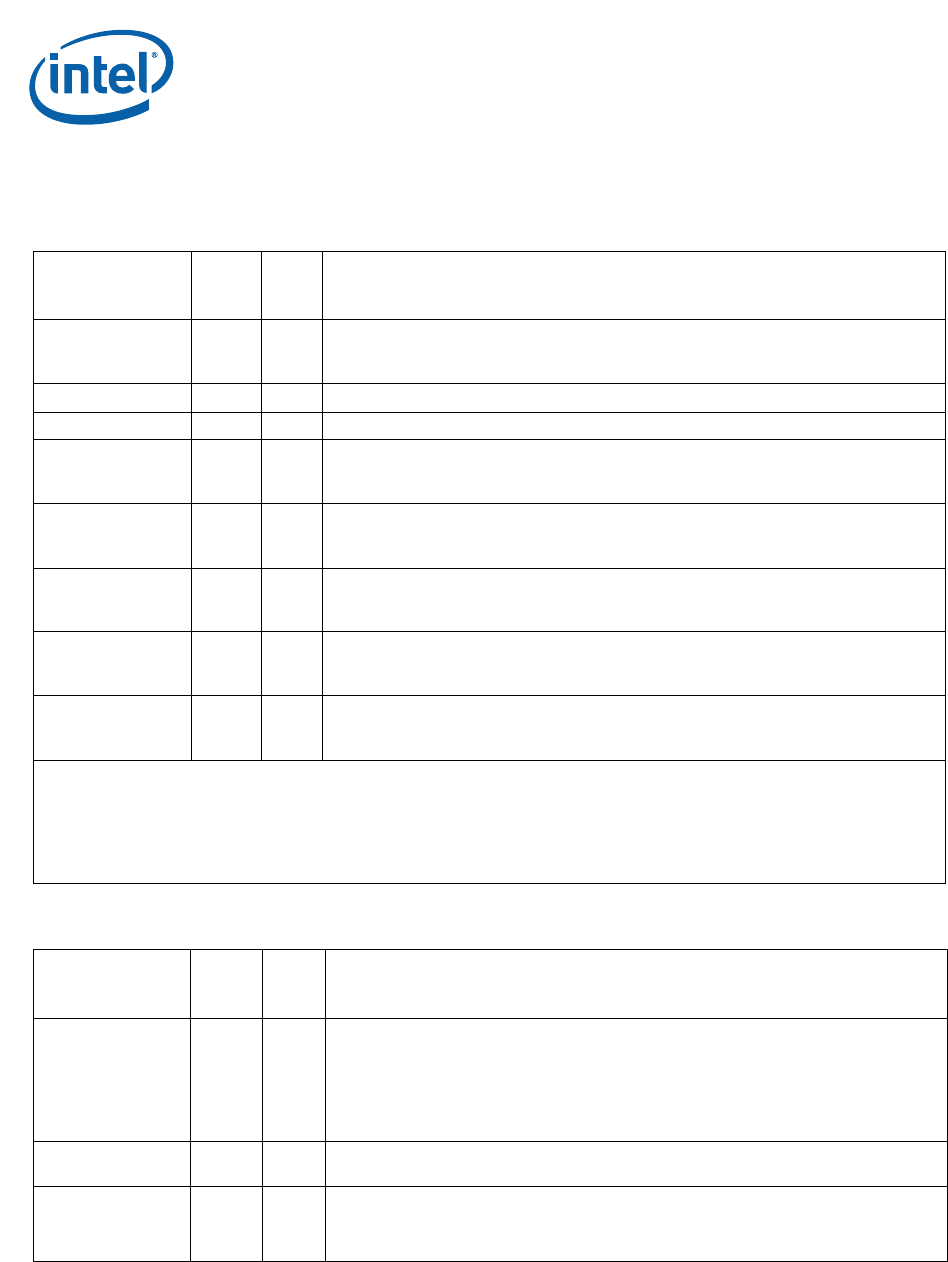

3.5.1 Signal Interface MII

Table 9. MII NPE A Signal Recommendations

Name

Type

Field

Pull

Up/

Down

Recommendations

ETHA_TXCLK I Yes

Transmit Clock.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

ETHA_TXDATA[3:0] O No Transmit Data.

ETHA_TXEN O No Transmit Enable.

ETHA_RXCLK I Yes

Receive Clock.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

ETHA_RXDATA[3:0] I Yes

Receive Data.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

ETHA_RXDV I Yes

Receive Data Valid.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

ETHA_COL I Yes

Collision Detect.

If operating in a full duplex mode and there is no requirement to use the Collision

Detect signal, then the pin must be pulled low with a 10-KΩ resistor.

ETHA_CRS I Yes

Carrier Sense.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Notes:

1. Features disabled/enabled by Soft Fuse must be done during the boot-up sequence. A feature cannot be enabled after

being disabled without asserting a system reset.

2. Features disabled by a specific part number, do not require pull-ups or pull-downs. Therefore, all pins can be left

unconnected.

3. Features enabled by a specific part number — and required to be Soft Fuse-disabled, as stated in Note 1 — only require

pull-ups or pull-downs in the clock-input signals.

Table 10. MII NPE C Signal Recommendations (Sheet 1 of 2)

Name

Type

Field

Pull

Up/

Down

Recommendations

ETHC_txclk I Yes

Externally supplied transmit clock.

• 25 MHz for 100 Mbps operation

• 2.5 MHz for 10 Mbps

This MAC contains hardware hashing capabilities that are local to the interface.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

ETHC_txdATA[3:0] O No

Transmit data bus to PHY, asserted synchronously with respect to ETHC_TXCLK. This

MAC contains hardware hashing capabilities that are local to the interface.

ETHC_txen O Yes

Indicates that the PHY is being presented with nibbles on the MII interface. Asserted

synchronously, with respect to ETHC_TXCLK, at the first nibble of the preamble, and

remains asserted until all the nibbles of a frame are presented. This MAC contains

hardware hashing capabilities that are local to the interface.